# Intel® 82803AA Memory Repeater Hub for RDRAM (MRH-R)

**Datasheet**

August 2000

Order Number: 298022 - 002

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 82803AA Memory Repeater Hub for RDRAM (MRH-R) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

$l^2C$  is a 2-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $l^2C$  bus/protocol and was developed by Intel. Implementations of the  $l^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Alert on LAN is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation www.intel.com

or call 1-800-548-4725

\*Third-party brands and names are the property of their respective owners.

Copyright © Intel Corporation 2000

# int<sub>e</sub>l. Contents

| 1. | Overv  | iew                                                          | 9        |

|----|--------|--------------------------------------------------------------|----------|

|    | 1.1.   | System Architecture                                          | 9        |

|    | 1.2.   | 'Expansion' Channel Interface                                | 10       |

|    | 1.3.   | MRH-R Direct RDRAM 'Stick' Channel Interface                 | 10       |

|    | 1.4.   | Register Interface                                           | 11       |

|    | 1.5.   | Terminology                                                  |          |

| 2. | Signal | Description                                                  | 13       |

|    | 2.1.   | 'Expansion' Channel Interface                                | 13       |

|    | 2.2.   | 'Stick' Channel A Interface                                  | 14       |

|    | 2.3.   | 'Stick' Channel B Interface                                  | 15       |

|    | 2.4.   | Miscellaneous Signals Interface                              | 15       |

|    |        | 2.4.1. MRH_SIO and SMBus Signal Interface                    | 15       |

|    |        | 2.4.2. Clocks, Reset, and Miscellaneous                      |          |

|    |        | 2.4.3. Voltage/Ground References                             | 16       |

| 3. | Regist | ter Description                                              | 17       |

|    | 3.1.   | MDID—MRH-R Device ID Register                                | 17       |

|    | 3.2.   | EXCC—Expansion Bus Current Control Register                  |          |

|    | 3.3.   | CACC—Channel A Current Control Register                      |          |

|    | 3.4.   | CBCC—Channel B Current Control Register                      |          |

|    | 3.5.   | SPDRDR—SPD Read Data and Status Register                     |          |

|    | 3.6.   | CCR—Clock Control Register                                   |          |

|    | 3.7.   | LMTR—Levelization Mode And Timing Register                   |          |

|    |        | 3.7.1. RIR—RAC Initialization Register                       |          |

|    | 3.8.   | RACAL—Stick Channel A RAC Configuration Low WORD Register    |          |

|    | 3.9.   | RACAH—Stick Channel A RAC Configuration High WORD Register   |          |

|    | 3.10.  | RACBL—Stick Channel B RAC Configuration Low Word Register    |          |

|    | 3.11.  | RACBH—Stick Channel B RAC Configuration High Word Register   |          |

|    | 3.12.  | RACXL—Expansion Channel RAC Configuration Low Word Register  |          |

|    | 3.13.  | RACXH—Expansion Channel RAC Configuration High Word Register |          |

|    | 3.14.  | INIT—MRH-R Initialization Register                           |          |

|    | 3.15.  | CNFGA—MRH-R Configuration Register                           |          |

|    | 3.16.  | ST—Stepping Register                                         |          |

| 4. | Functi | onal Description                                             | 27       |

|    | 4.1.   | MRH-R and the Direct RDRAM Channel                           | 27       |

|    |        | 4.1.1. Operation Overview                                    |          |

|    |        | 4.1.2. Signal and Protocol Overview                          | 27       |

|    |        | 4.1.2.1. Refresh and Post-Refresh Precharge                  | 28       |

|    |        | 4.1.2.2. Power Mode Control                                  | 28       |

|    |        | 4.1.2.3. Current Calibration                                 |          |

|    |        | 4.1.2.4. Thermal Sensor Read                                 |          |

|    |        | 4.1.2.5. Temperature Calibration                             | 29<br>29 |

|    |        |                                                              |          |

|    |        |          | 4.1.3.1.   | Overview                                 | 29 |

|----|--------|----------|------------|------------------------------------------|----|

|    |        |          | 4.1.3.2.   | Packet Formats                           |    |

|    |        |          | 4.1.3.3.   | Transactions                             | 33 |

|    |        |          | 4.1.3.4.   | Levelization                             |    |

|    |        |          | 4.1.3.5.   | Initialization                           |    |

|    |        |          | 4.1.3.6.   | MRH-R Register Operations                |    |

|    |        |          | 4.1.3.7.   | RDRAM Register Operations                | 35 |

|    |        | 4.1.4.   | SMBU       | JS Operation                             | 35 |

|    |        |          | 4.1.4.1.   | SIO Request Packet for SPD Random Read   |    |

|    |        |          | 4.1.4.2.   | SIO Request Packet for SPD Write Command | 37 |

|    |        |          | 4.1.4.3.   | Command Protocol and Bus Timing          | 38 |

|    | 4.2.   |          |            |                                          |    |

|    | 4.3.   | Power    | Managem    | ent                                      | 39 |

|    | 4.4.   | STR S    | support    |                                          | 39 |

| 5. | Ballou | t and Pa | ckage Info | rmation                                  | 41 |

|    | 5.1.   | MRH-F    | R Ballout  |                                          | 41 |

|    | 5.2.   |          |            | ations                                   |    |

|    | 5.3.   |          |            | malized Trace Length Data                |    |

| 6. | Testal | oility   |            |                                          | 51 |

|    | 6.1.   | Tri-sta  | te Mode    |                                          | 51 |

|    | 6.2.   | XOR C    | Chain Mode | )                                        | 51 |

### **Figures**

| Figure 1. Intel <sup>®</sup> 840 Chipset Memory Subsystem with MRH-Rs | 9  |

|-----------------------------------------------------------------------|----|

| Figure 2. 82840 MCH to 82803AA MRH-R Interconnect Diagram             |    |

| Figure 3. Connection of CMOS Signals                                  |    |

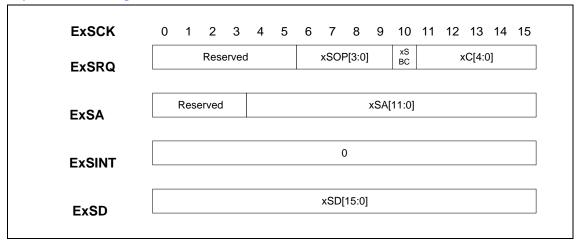

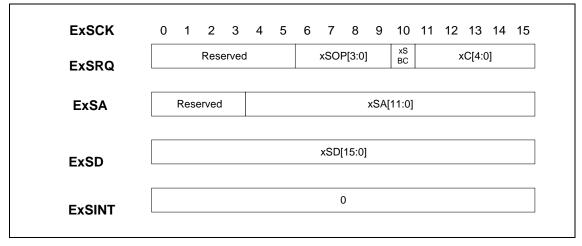

| Figure 4. Expansion Bus Register Read Packet Format                   | 31 |

| Figure 5. Expansion Bus Register Write Packet Format                  | 31 |

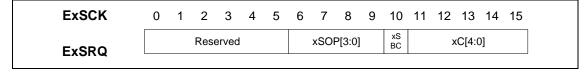

| Figure 6. Expansion Bus Non-Register Operation Packet Format          | 31 |

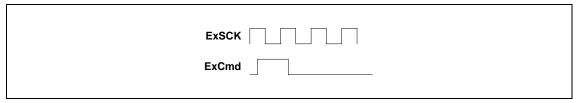

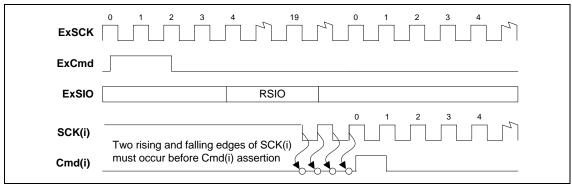

| Figure 7. ExSIO Reset Sequence                                        | 33 |

| Figure 8. RDRAM SIO Reset Sequence                                    | 33 |

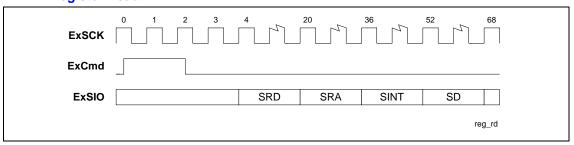

| Figure 9. MRH-R Register Read                                         |    |

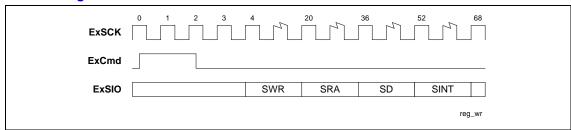

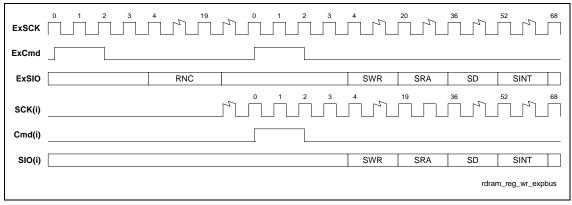

| Figure 10. MRH-R Register Write                                       | 34 |

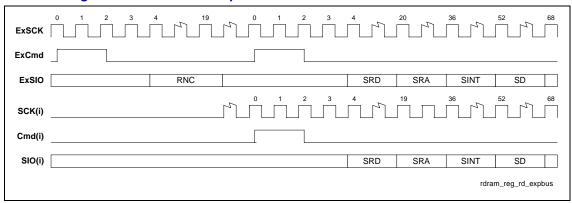

| Figure 11. RDRAM Register Read from the Expansion Serial Bus          |    |

| Figure 12. RDRAM Register Write from the Expansion Serial Bus         |    |

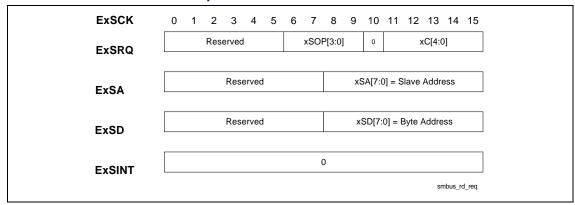

| Figure 13. SMBUS SIO Random Read Request Packet Format                |    |

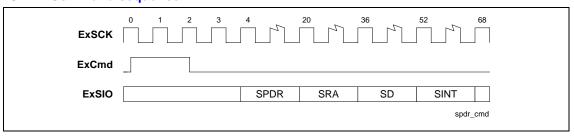

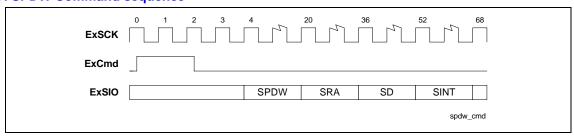

| Figure 14. SPDR Command sequence                                      |    |

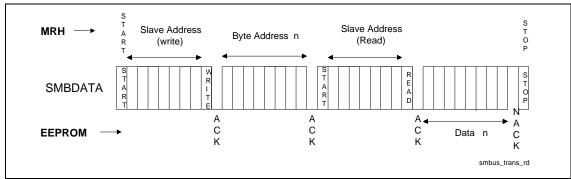

| Figure 15. SMBUS Transactions to Read EEPROM                          |    |

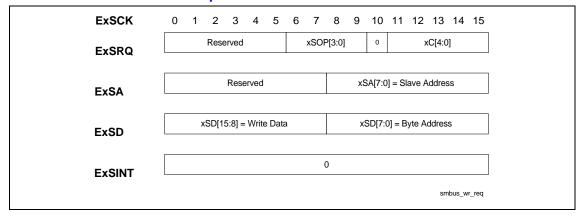

| Figure 16. SMBUS SIO Random Write Request Packet Format               |    |

| Figure 17. SPDW Command sequence                                      |    |

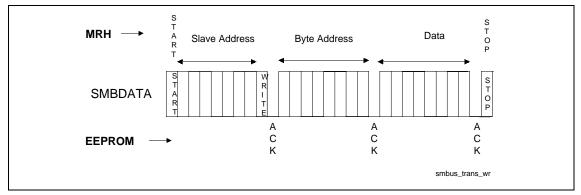

| Figure 18. SMBUS Transactions to Write to EEPROM                      |    |

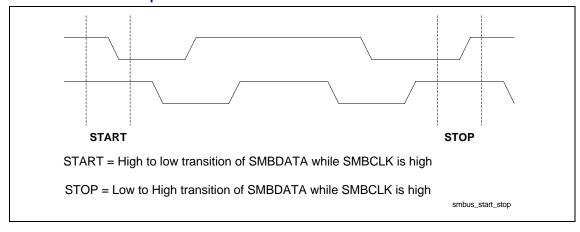

| Figure 19. SMBUS Start and Stop Conditions                            |    |

| Figure 20. MRH-R Ballout (Top View, Left Side)                        |    |

| Figure 21. MRH-R Ballout (Top View, Right Side)                       |    |

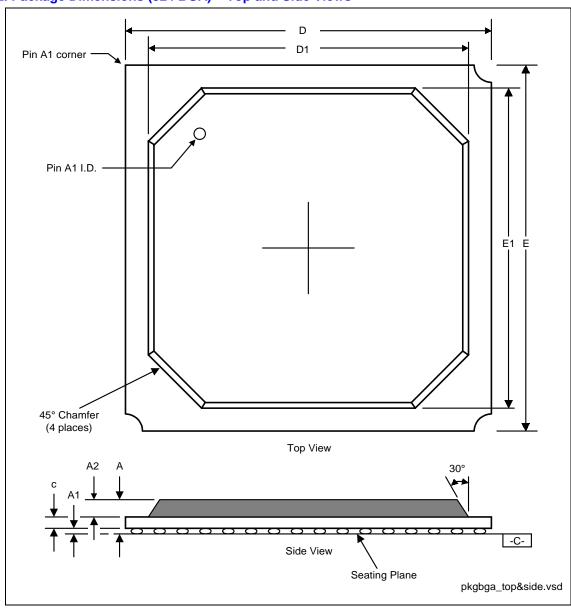

| Figure 22. Package Dimensions (324 BGA) – Top and Side Views          |    |

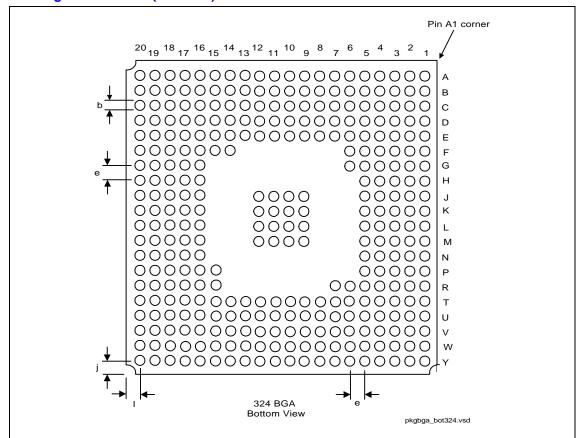

| Figure 23. Package Dimensions (324 BGA) – Bottom View                 | 47 |

|                                                                       |    |

### **Tables**

| Table 1. Maximum Memory Support                        | 9  |

|--------------------------------------------------------|----|

| Table 2. Expansion Bus Serial Packet Field Definitions |    |

| Table 3. Read Byte Protocol                            |    |

| Table 4. MRH-R Alphabetical Ball Assignment            |    |

| Table 5. BGA Package Dimensions (324 BGA)              |    |

| Table 6. MRH-S RSL Normalized Trace Length Data        |    |

| Table 7. MRH-R Test Modes                              |    |

| Table 8. MRH-R XOR Chains                              | 52 |

### **Revision History**

| Rev. | Description                                                                            | Date         |

|------|----------------------------------------------------------------------------------------|--------------|

| -001 | Initial Release                                                                        | January 2000 |

| -002 | Removed support for 2 MRH-Rs per MCH channel. MCH only supports one MRH-R per channel. | August 2000  |

|      | Minor Edits for clarity                                                                |              |

## Intel® 82803AA Memory Repeater Hub for RDRAM (MRH-R)

### **Product Features**

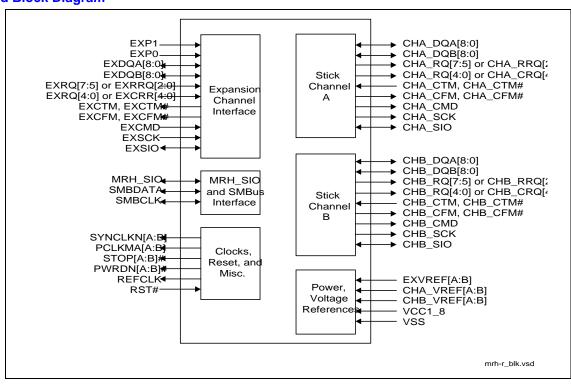

- Supports two Direct RDRAM 'stick' channels and one 'expansion' channel.

- Pass through architecture for Read and Write accesses.

- Supports 64Mbit, 128Mbit, and 256Mbit RDRAM technologies.

- Maximum Memory Array Sizes: Up to 1 GB using 64Mbit RDRAM devices, 2 GB using 128Mbit RDRAM devices, and 4 GB using 256Mbit RDRAM devices.

- Integrates logic to do Nap Exit, Powerdown Exit, Refresh, and Post-Refresh Precharge on a channel upon request from the Memory Controller Hub (MCH).

- Integrates logic to do 'expansion' channel and 'stick' channel current calibration

- Support of 2 wire RSL sideband channel to support up to two MRH-Rs per 'expansion' channel in the memory array.

- Integrates control of 2 external DRCG clock generators.

- 6 rclk round trip delay for RSL signals through the MRH-R

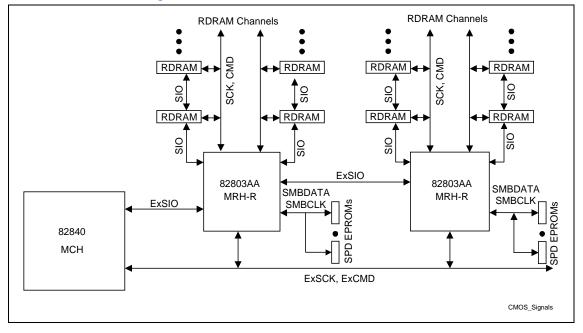

- Support of RDRAM CMOS signals to facilitate initialization, read/write of registers and Nap and Powerdown exits.

- MRH-R internal registers accessed through CMOS signal interface

- Integrated System Management Bus (SMB) controller to read and write data from/to SPD EEPROM on the RIMMs

- 324 pin miniBGA

The Intel® 82803AA Memory Repeater Hub for RDRAM (MRH-R) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

### **Simplified Block Diagram**

### 1. Overview

### 1.1. System Architecture

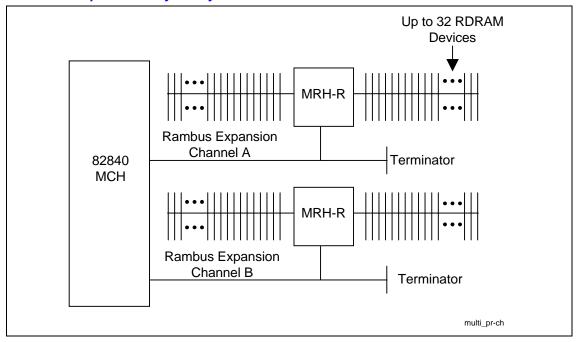

The 'Expansion' channel is the interconnect between the MCH and the MRH-R. The MRH-R component provides the capability to support multiple Direct RDRAM channels off each 'expansion' channel of a MCH.

As an example, the Intel<sup>®</sup> 82840 MCH supports one MRH-R on each of its 'expansion' channel buses for a maximum of two MRH-Rs in an Intel<sup>®</sup> 840 chipset system memory array.

*Note:* Future Intel chipsets will support the MRH-Rs as well.

**Table 1. Maximum Memory Support**

| RDRAM<br>Technology | Max Memory w/ one<br>MRH-R | Max Memory w/ two<br>MRH-Rs |

|---------------------|----------------------------|-----------------------------|

| 64Mbit              | 512 MB                     | 1 GB                        |

| 128Mbit             | 1 GB                       | 2 GB                        |

| 256Mbit             | 2 GB                       | 4 GB                        |

Figure 1 is a block diagram of an Intel<sup>®</sup> 840 memory subsystem using two MRH-Rs per 'expansion' channel to support four Direct RDRAM Channels.

Figure 1. Intel® 840 Chipset Memory Subsystem with MRH-Rs

### 1.2. 'Expansion' Channel Interface

The 'expansion' channel is the interconnection between the MCH and the MRH-R. The 'expansion' channel is a superset of the Direct RDRAM channel. In addition to the Direct RDRAM channel signals, the 'expansion' channel has two RSL signals to communicate channel and control information from the MCH to the MRH-R. These two signals are known as expansion control signals, EXP0 and EXP1.

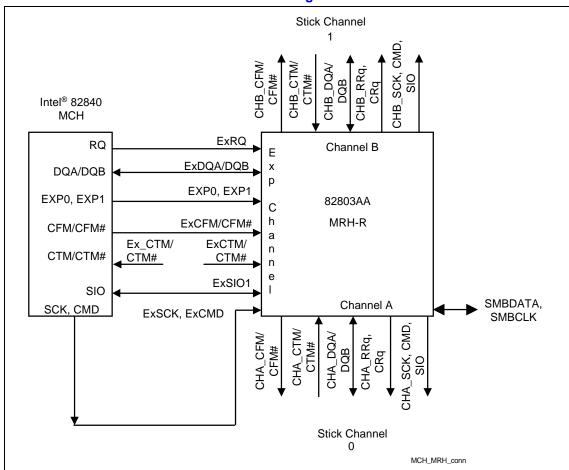

The 'expansion' channel interface consists of 28 RSL, 4 clock and 3 CMOS signals. Figure 2 shows the interface signals between the MCH and the MRH-R.

Figure 2. 82840 MCH to 82803AA MRH-R Interconnect Diagram

### 1.3. MRH-R Direct RDRAM 'Stick' Channel Interface

The MRH-R supports two Direct RDRAM channels referred to as Channel A (CHA) and Channel B (CHB) as shown in Figure 2. These two channels are also referred to as 'Stick' Channel A and 'Stick' Channel B. Each 'stick' channel interface consists of 26 RSL, 4 clock and 3 CMOS signals, and supports up to 32 RDRAM devices.

### 1.4. Register Interface

The MRH-R has internal configuration and control registers. These registers are accessed through the SCK, CMD and SIO CMOS signal interface (ExSCK, ExCMD, and ExSIO for the 'Expansion' Channel). The internal registers in the RDRAM devices are also accessed through the same CMOS signal interface (CHA\_SCK, CHA\_CMD, and CHA\_SIO for 'Stick' Channel A; CHB\_SCK, CHA\_CMD, and CHB\_SIO for 'Stick' Channel B).

In addition, the MRH-R also provides a System Management Bus (SMBus) interface to read the SPD EEPROM on the RIMM module. The SMBus interface consists of two CMOS signals, SMBDATA and SMBCLK.

### 1.5. Terminology

#### **RAMBUS\***

RSL Rambus\* Signaling Level is the name of the signaling technology used

by Rambus\*.

Rclk Rclk refers to the RSL bus' high speed clock in a generic fashion, often

in the context of clock counts in timing specs.

RAC Rambus\* ASIC Cell. It is the embedded cell designed by Rambus\* that

interfaces with the Rambus\* devices using RSL signaling.

RMC Rambus\* Memory Controller. This is the logic that directly interfaces to

the RAC.

RIMM Rambus\* Interface Memory Module.

Components

Intel<sup>®</sup> 82840 MCH The Memory Controller Hub component that contains the CPU

interface, Rambus\* controller, and AGP interface. It communicates with

the ICH over a proprietary interconnect called Hub Interface.

Intel® 82803AA MRH-R The Memory Repeater Hub for RDRAM.

'Expansion' Channel The RSL bus which connects the Memory Controller Hub to the

MRH-R.

'Stick' Channel The pair of RSL busses which connects an MRH-R to its RDRAM

devices. An MRH-R can support a maximum of 2 'stick' channels,

'Stick' Channel A and 'Stick' Channel B.

This page is left intentionally blank.

### 2. Signal Description

### 2.1. 'Expansion' Channel Interface

| Signal                   | Туре        | Description                                                                                                                                                                                            |

|--------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXP1                     | l<br>RSL    | <b>Expansion Row Control.</b> This signal carries the row control packets (ExRCP) from the MCH to attached MRH-Rs.                                                                                     |

| EXP0                     | I<br>RSL    | <b>Expansion Column Control.</b> This signal carries the column control packets (ExCCP) from the MCH to attached MRH-Rs.                                                                               |

| ExDQA[8:0]               | I /O<br>RSL | <b>Expansion Data Bus (Data Byte A).</b> Bi-directional 9 bit data bus A. These correspond to the CHx_DQA[8:0] signals on the Direct RDRAM 'Stick' Channels.                                           |

| ExDQB[8:0]               | I/O<br>RSL  | <b>Expansion Data Bus (Data Byte B).</b> Bi-directional 9 bit data bus B. These correspond to the CHx_DQB[8:0] signals on the Direct RDRAM 'Stick' Channels.                                           |

| ExRQ[7:5]/<br>ExRRq[2:0] | l<br>RSL    | <b>Expansion Row Request.</b> These signals carry row request packets from the MCH to the MRH-Rs. These correspond to the CHx_RQ[7:5]/CHx_RRq[2:0] signals on the Direct RDRAM 'Stick' Channels.       |

| ExRQ[4:0]/<br>ExCRq[4:0] | l<br>RSL    | <b>Expansion Column Request.</b> These signals carry column request packets from the MCH to the MRH-Rs. These correspond to the CHx_RQ[4:0]/CHx_CRq[4:0] signals on the Direct RDRAM 'Stick' Channels. |

| ExCTM                    | l<br>RSL    | <b>Expansion Clock To MCH.</b> One of the two differential transmit clock signals used for MRH-R to MCH operations.                                                                                    |

| ExCTM#                   | I<br>RSL    | <b>Expansion Clock To MCH Complement.</b> One of the two differential transmit clock signals used for MRH-R to MCH operations.                                                                         |

| ExCFM                    | l<br>RSL    | <b>Expansion Clock from MCH.</b> One of the differential receive clock signals used for MCH to MRH-R operation.                                                                                        |

| ExCFM#                   | I<br>RSL    | <b>Expansion Clock From MCH Complement.</b> One of the differential receive clock signals used for MCH to MRH-R operation.                                                                             |

| ExSIO                    | I/O<br>CMOS | <b>Expansion Serial IO Chain.</b> Serial input/output pins used for reading and writing control registers. These correspond to the SIO signals on the Direct RDRAM 'Stick' Channels.                   |

| ExSCK                    | I<br>CMOS   | <b>Expansion Serial Clock.</b> Clock source used to used for timing of the ExSIO and ExCMD signals. This corresponds to the SCK signal on the Direct RDRAM 'Stick' Channels.                           |

| ExCMD                    | I<br>CMOS   | <b>Expansion Serial Command.</b> Serial command input used for control register read and write operations. This corresponds to the CMD signal on the Direct RDRAM 'Stick'Channels.                     |

### 2.2. 'Stick' Channel A Interface

| Signal                       | Туре        | Description                                                                                                                                                           |

|------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHA_DQA[8:0]                 | I/O RSL     | Channel A RDRAM Data Bus (Data Byte A). Bi-directional 9 bit (8 data plus one parity) data bus A.                                                                     |

| CHA_DQB[8:0]                 | I/O RSL     | <b>Channel A RDRAM Data Bus (Data Byte B).</b> Bi-directional 9 bit (8 data plus one parity) data bus B.                                                              |

| CHA_RQ[7:5]/<br>CHA_RRq[2:0] | O<br>RSL    | <b>Channel A Row Request.</b> RQ[7:5]/RRq[2:0] are used to transmit Row Request Packets to RDRAM                                                                      |

| CHA_RQ[4:0]/<br>CHA_CRq[4:0] | O<br>RSL    | <b>Channel A Column Request.</b> RQ[4:0]/CRq[4:0] are used to transmit column request packets to RDRAM.                                                               |

| CHA_CTM                      | I<br>RSL    | Channel A Clock To MRH-R. One of the two differential receive clock signals used for RDRAM to MRH-R operation.                                                        |

| CHA_CTM#                     | I<br>RSL    | Channel A Clock To MRH-R Complement. One of the two differential receive clock signals used for RDRAM to MRH-R operation.                                             |

| CHA_CFM                      | O<br>RSL    | Channel A Clock From MRH-R. One of the differential transmit clock signals used for MRH-R to RDRAM operation.                                                         |

| CHA_CFM#                     | O<br>RSL    | Channel A Clock From MRH-R Complement. One of the differential transmit clock signals used for MRH-R to RDRAM operation.                                              |

| CHA _CMD                     | O<br>CMOS   | <b>Channel A Command.</b> This signal is used for SIO framing sequence, pin initialization and power management.                                                      |

| CHA_SCK                      | O<br>CMOS   | Channel A Serial Clock. The signal provides SIO clocking for register accesses and selects RDRAM devices for power management.                                        |

| CHA_SIO                      | I/O<br>CMOS | Channel A Serial Input and Output. This bi-directional signal is used to carry data for SIO operations: register accesses, device reset and device ID initialization. |

### 2.3. 'Stick' Channel B Interface

| Signal                       | Туре        | Description                                                                                                                                                                |

|------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHB_DQA[8:0]                 | I/O<br>RSL  | Channel B RDRAM Data Bus, Data Byte A. Bi-directional 9 bit (8 data plus one parity) data bus A.                                                                           |

| CHB_DQB[8:0]                 | I/O<br>RSL  | <b>Channel B RDRAM Data Bus, Data Byte B.</b> Bi-directional 9 bit (8 data plus one parity) data bus B.                                                                    |

| CHB_RQ[7:5]/<br>CHB_RRq[2:0] | O<br>RSL    | Channel B Row Request. RQ[7:5]/RRq[2:0] are used to transmit Row Request Packets to RDRAM                                                                                  |

| CHB_RQ[4:0]/<br>CHB_CRq[4:0] | O<br>RSL    | <b>Channel B Column Request.</b> RQ{4:0]/CRq[4:0] are used to transmit column request packets to RDRAM.                                                                    |

| CHB_CTM                      | I<br>RSL    | Channel B Clock To MRH-R. One of the two differential receive clock signals used for RDRAM to MRH-R operation.                                                             |

| CHB_CTM#                     | I<br>RSL    | Channel B Clock To MRH-R Complement. One of the two differential receive clock signals used for RDRAM to MRH-R operation.                                                  |

| CHB_CFM                      | O<br>RSL    | Channel B Clock From MRH-R. One of the differential transmit clock signals used for MRH-R to RDRAM operation.                                                              |

| CHB_CFM#                     | O<br>RSL    | Channel B Clock From MRH-R Complement. One of the differential transmit clock signals used for MRH-R to RDRAM operation.                                                   |

| CHB_CMD                      | O<br>CMOS   | Channel B Command. This signal is used for SIO framing sequence, pin initialization and power management.                                                                  |

| CHB_SCK                      | O<br>CMOS   | Channel B Serial Clock. The signal provides SIO clocking for register accesses and selects RDRAM devices for power management.                                             |

| CHB_SIO                      | I/O<br>CMOS | Channel B Serial Input and Output. These bi-directional signals are used to carry data for SIO operations (register accesses, device reset, and device ID initialization). |

### 2.4. Miscellaneous Signals Interface

### 2.4.1. MRH\_SIO and SMBus Signal Interface

| Signal  | Туре        | Description                                                                                                                                                                                                |

|---------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MRH_SIO | I/O<br>CMOS | MRH-R Serial Input and Output. This bi-directional signal is used to carry data for SIO operations between MRH-Rs. These operations include: register accesses, device reset and device ID initialization. |

| SMBDATA | I/O<br>CMOS | SM Bus Data. SM bus data.                                                                                                                                                                                  |

| SMBCLK  | I/O<br>CMOS | SM Bus Clock. SM bus clock.                                                                                                                                                                                |

### 2.4.2. Clocks, Reset, and Miscellaneous

| Signal   | Туре      | Description                                                                                                                                               |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYNCLKNA | O<br>CMOS | Phase Detector Input to DRCG. This signal is connected to the SYNCLKN pin of the DRCG (Direct Rambus* Clock Generator) used for clocking RDRAM channel A. |

| SYNCLKNB | O<br>CMOS | Phase Detector Input to DRCG. This signal is connected to the SYNCLKN pin of the DRCG (Direct Rambus* Clock Generator) used for clocking RDRAM channel B. |

| PCLKMA   | O<br>CMOS | Phase Detector Input to DRCG. This signal is connected to the PCLKM pin of the DRCG (Direct Rambus* Clock Generator) used for clocking RDRAM channel A.   |

| PCLKMB   | O<br>CMOS | Phase Detector Input to DRCG. This signal is connected to the PCLKM pin of the DRCG (Direct Rambus* Clock Generator) used for clocking RDRAM channel B.   |

| STOPA#   | O<br>CMOS | DRCG A STOP Signal. This signal is connected to the DRCG's STOP# input corresponding to stick channel A.                                                  |

| STOPB#   | O<br>CMOS | DRCG B STOP Signal. This signal is connected to the DRCG's STOP# input corresponding to stick channel B.                                                  |

| PWRDNA#  | O<br>CMOS | DRCG A PWRDN Signal. This signal is connected to the DRCG's PWRDN# input corresponding to stick channel A.                                                |

| PWRDNB#  | O<br>CMOS | DRCG B PWRDN Signal. This signal is connected to the DRCG's PWRDN# input corresponding to stick channel B.                                                |

| REFCLK   | O<br>CMOS | Reference Clock to DRCGs. This pin is connected to the REFCLK inputs on both DRCGs.                                                                       |

| RST#     | I<br>CMOS | <b>Reset.</b> When asserted, this signal asynchronously resets the MRH-R logic. This is the system reset signal used for resetting the MCH, ICH, etc.     |

### 2.4.3. Voltage/Ground References

| Signal                                          | Description                                                                                                     |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| EXVREF[A:B],<br>CHA_VREF[A:B],<br>CHB_VREF[A:B] | RDRAM Reference Voltage[1.4V]. RSL reference voltage for 'expansion' channel and Direct RDRAM 'Stick' channels. |

| VCC1_8                                          | 1.8V Power Pins. Power pins for RSL interface.                                                                  |

| VSS                                             | Ground Pins. Ground pins for RSL interface.                                                                     |

### 3. Register Description

### 3.1. MDID—MRH-R Device ID Register

Address: 02h Default: 04C0h

Access: R/W (bits 5:14 are read only)

Size: 16 bits

| Bit   | Descriptions                                                                                                                                                                                                                                |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:13 | Reserved                                                                                                                                                                                                                                    |

| 12:10 | <b>Channel ID Mask.</b> This field is used to mask the MRH-R ID bits from the Device ID to get the channel ID. Device ID bits 2:1 are used for MRH-R ID. When a mask bit has a value of 0, it masks the corresponding bit in the device ID. |

|       | 001 = This field is hardwired to 001.                                                                                                                                                                                                       |

| 9:8   | Reserved                                                                                                                                                                                                                                    |

| 7:5   | MRH-R ID Mask. This field is used to mask the channel ID bits from the Device ID to derive the MRH-R ID. The Device ID bit 0 is used for channel ID. When a mask bit has a value of 0, it masks the corresponding bit in the device ID.     |

|       | 110 = This field is hardwired to 110.                                                                                                                                                                                                       |

| 4:3   | Reserved                                                                                                                                                                                                                                    |

| 2:0   | <b>Device ID.</b> This field specifies the device ID of the MRH-R. The device ID is compared against the device ID in the ExRCP and ExCCP packets to determine if this is the addressed MRH-R device.                                       |

### 3.2. EXCC—Expansion Bus Current Control Register

Address: 04h

Default: 0000h

Access: Read / Write

Size: 16 bits

| Bit   | Description                                                                                                                                                                                                                                                                                                                      |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 | Reserved                                                                                                                                                                                                                                                                                                                         |

| 10    | <b>Enable Stick Channel B.</b> When this bit is set to 0, all the logic and circuits including DLLs and clock generator associated with channel B are turned off. This bit must not be turned on and off dynamically. Once the BIOS determines there are devices on channel B it can set this bit to 1 to activate that channel. |

| 9     | <b>Enable Stick Channel A.</b> When this bit is set to 0, all the logic and circuits including DLLs and clock generator associated with channel A are turned off. This bit must not be turned on and off dynamically. Once the BIOS determines there are devices on channel A it can set this bit to 1 to activate that channel. |

| 8:7   | Reserved                                                                                                                                                                                                                                                                                                                         |

| 6:0   | Current Control A. This seven bit field controls the current for the EXDQA[8:0] and EXDQB[8:0] 'expansion' channel RSL pins.                                                                                                                                                                                                     |

### 3.3. CACC—Channel A Current Control Register

Address: 06h

Default: 0000h

Access: Read / Write

Size: 16 bits

| Bit  | Description                                                                                                                  |

|------|------------------------------------------------------------------------------------------------------------------------------|

| 15:7 | Reserved                                                                                                                     |

| 6:0  | Current Control A. This seven bit field controls the current for the CHA_DQA[8:0] and CHA_DQB[8:0] 'stick' channel RSL pins. |

### 3.4. CBCC—Channel B Current Control Register

Address: 08h

Default: 0000h

Access: Read/Write

Size: 16 bits

| Bit  | Description                                                                                                                  |

|------|------------------------------------------------------------------------------------------------------------------------------|

| 15:9 | Reserved                                                                                                                     |

| 8:7  | Reserved                                                                                                                     |

| 6:0  | Current Control A. This seven bit field controls the current for the CHB_DQA[8:0] and CHB_DQB[8:0] 'stick' channel RSL pins. |

### 3.5. SPDRDR—SPD Read Data and Status Register

Address: 0Ah

Default: 0000h

Access: Read/Write

Size: 16 bits

| Bit  | Description                                                                                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | Read Data Status.                                                                                                                                                                                                                         |

|      | 1 = The SPD Read Data located in bits[7:0] of this register, is valid.                                                                                                                                                                    |

|      | 0 = This bit is cleared when this register is read by the MCH.                                                                                                                                                                            |

| 14   | Write Operation Done.                                                                                                                                                                                                                     |

|      | 1 = Set by MRH-R when the SPDW command execution is successfully completed on the SMBUS.                                                                                                                                                  |

|      | 0 = Cleared when this register is read by the MCH.                                                                                                                                                                                        |

| 13   | SMBUS Error.                                                                                                                                                                                                                              |

|      | 1 = Set by the MRH-R if the transaction initiated on the SMBUS did not complete successfully.                                                                                                                                             |

|      | 0 = Cleared when this register is read by the MCH.                                                                                                                                                                                        |

| 12:8 | Reserved                                                                                                                                                                                                                                  |

| 7:0  | SPD Register Read/Write Data. This field contains the data read from the EEPROM due to an SPDR command issued by the MCH. This data field is valid only when the "Read Data Status" bit (bit 15 of this register) has a logic value of 1. |

### 3.6. CCR—Clock Control Register

Address: 0Bh

Default: 0000h (bit '0' is Read Only)

Access: Read/Write Size: 16 bits

| Bit  | Description                                                                                                                                                                                                                                      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:6 | Reserved                                                                                                                                                                                                                                         |

| 5    | <b>DRCG B STOP#.</b> This bit is directly connected to the STOPB# pin on the MRH-R. This pin is then connected to the STOP# pin on the channel B DRCG.                                                                                           |

| 4    | <b>DRCG B PWRDN#</b> . This bit is directly connected to the PWRDNB# pin on the MRH-R. The PWRDNB# pin is connected to the channel B external DRCG PWRDN# pin. Note that this pin defaults to '0' so that the DRCG is disabled at powerup.       |

| 3    | <b>DRCG A STOP#.</b> This bit is directly connected to the STOPA# pin on the MRH-R. This pin is then connected to the STOP# pin on the channel A DRCG.                                                                                           |

| 2    | <b>DRCG A PWRDN#.</b> This bit is directly connected to the PWRDNA# pin on the MRH-R. The PWRDNA# pin is connected to the PWRDN# pin on the channel A external DRCG. Note that this pin defaults to '0' so that the DRCG is disabled at powerup. |

| 1    | <b>External Clock Generation.</b> When set to '1', this bit indicates that external DRCGs will generate the clocks for 'stick' channels A and B.                                                                                                 |

| 0    | Expansion Skip Status Bit (ESS). This bit contains a value indicating the phase relationship of the CFM/CTM clocks.                                                                                                                              |

### 3.7. LMTR—Levelization Mode And Timing Register

Address: 0Eh Default: 0000h

Access: Bit 15 read only, bits 14:12 write-only, bits 11:8, 7, 6:4, 3:0 are write-gated

Size: 16 bits

| Bit | Description                                                                 |

|-----|-----------------------------------------------------------------------------|

| 15  | Levelization Mode Status (LMS)—RO.                                          |

|     | 1 = MRH-R is in levelization mode. (i.e., via SLM command described below.) |

|     | 0 = Normal operation for the MRH-R.                                         |

| Bit   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14:12 | Levelization Commands (LCMD).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 000 = <b>NOP.</b> no command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 001 = Write to tCAC field (W_TCAC). write-enables the tCAC field (bits 11:8) in this register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | 010 = Write to tRDLY field (W_TRDLY). write-enable for tRDLY field (bits 6:4). This field can be written to in levelization or non-levelization mode. However, while in levelization mode, the value contained in this register will NOT affect 'stick' channel read delay towards the 'expansion' channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 011 = Write to tRDLY_stick field (W_STRDLY). tRDLY_stick field (bits 2:0) are written. In this case, the measured value during levelization is overwritten. If the MRH-R is in levelization mode, then this command has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 100 = Write to clock frequency bit (W_FREQ). The MCH writes to Bit 7 of this register before RAC initialization to determine the RDRAM Clock Frequency for the MRH-R.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 101 = Write ALL Fields (W_ALL). Causes all fields (tCAC, tRDLY, tRDLY_stick, and frequency) to be written to. Can be used for R/W testing of the register bits. Note that the tRDLY_stick field write restriction still applies while in levelization mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 110 = Clear Levelization Mode (CLM). Causes the MRH-R to exit levelization mode. The last measured read data delay value during levelization - the tCAC value in bits 11:8 of this register will be contained in the tRDLY_stick bits. During normal mode, the value of the tRDLY register will now also affect the delay in the MRH-R read FIFO unload to the 'expansion' bus (which effectively delays read data towards the MCH).                                                                                                                                                                                                                                                                                                                                                                             |

|       | 111 = Set Levelization Mode (SLM). This command causes the MRH-R to enter levelization mode. In this mode, read data delay from the 'stick' channels to the 'expansion' channel remains fixed at 3 rclks – tTR, regardless of the value in the MRH-R tRDLY register and the tRDLY_stick field of this register. The MRH-R also starts measuring (on-the-fly), the # rclks from an expansion SCP read command to when a leading '1' bit is detected in the internal read path from either 'stick' channel on 'stick' channel data signal DQA5, or in other words, the 'stick' channel's read delay. The desired read to be measured is to the last (furthest) RDRAM on the 'stick' channel.                                                                                                                       |

| 11:8  | RDRAM tCAC read access delay (tCAC). (Write-gated by W_TCAC above). This field defines the minimum delay in rclks for RDRAMs from a Read SCP command to read data on the 'stick' channels (4-9). Values of 0-3, and A-Fh are illegal. The MRH-R must use this parameter to time its read data path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7     | RDRAM Clock Frequency (freq). (Write-gated by W_FREQ above]. Must be set to proper value before RAC initialization begins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | 0 = 300 MHz bus operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | 1 = 400 MHz bus operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6:4   | <b>Expansion Channel Time Domains (tRDLY).</b> [Write-gated by W_TRDLY above]. This field controls the read data delay from the MRH-R to the 'expansion' channel. Its purpose is to allow time domain equalization to be achieved among ALL 'stick' channels behind ALL MRH-Rs to the MCH. During levelization, the value of this register will not affect read data delay thru the MRH-R which remains fixed at 3-tTR rclks. In normal operation, its value will add to the total read data delay from all RDRAM devices on the MRH-R's 'stick' channels to the MCH. It is written to using the W_TRDLY command (see above) via a CMOS serial write to this register.                                                                                                                                           |

| 3     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2:0   | Stick Channel Time Domains (tRDLY_stick). (Write-gated by W_STRDLY above). This field is written to by the MRH-R itself while in levelization mode with a measured delay (0-7 rclks) from a 'stick' channel SCP read packet to the first non-zero data seen on 'stick' channel signal DQA5 at the MRH-R 'stick' channel interfaces. It is used internally by the MRH-R primarily to control its read data delay FIFO loading and to control the 'stick' channels to 'expansion' channel data steering mux. It can also be written to using a W_STRDLY command (see above) via a CMOS serial write to this register, but while the MRH-R is in levelization mode, it is Read-Only (ie. wrt CMOS bus). BIOS can read this field to determine the number of time domains on the addressed MRH-R's 'stick' channels. |

### 3.7.1. RIR—RAC Initialization Register

Address: 0Fh

Default: 0000h

Access: Read/Write

Size: 16 bits

| Bit  | Description                                                                                                                                                                                                                                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:5 | Reserved.                                                                                                                                                                                                                                                                                                                                      |

| 4    | RAC Initialization Complete (RC). The MRH-R sets this bit after it has completed RAC initialization.  BIOS must check this bit to make sure the RACs have been properly initialized before initiating memory accesses.                                                                                                                         |

|      | 1 = Initialization Complete                                                                                                                                                                                                                                                                                                                    |

|      | 0 = Initialization not Complete                                                                                                                                                                                                                                                                                                                |

| 3    | Initiate RIC operation (IRO). BIOS must check that this bit is 0 before writing to this bit again.                                                                                                                                                                                                                                             |

|      | 1 = Execution In-Progress. Execution of the RIC command specified by bits 2:0 begins.                                                                                                                                                                                                                                                          |

|      | 0 = Execution Complete. After the operation is completed, the MRH-R clears this bit to 0.                                                                                                                                                                                                                                                      |

| 2:0  | RAC Initialization Command (RIC). This field allows BIOS to initialize the MRH-R RACs. BIOS programs this field with the appropriate command then sets bit 3 to 1. The MRH-R then executes the command specified in this field. When the operation is complete, the MRH-R clears bit 3 to 0.                                                   |

|      | 000 = Reserved                                                                                                                                                                                                                                                                                                                                 |

|      | 001 = Initialize Expansion RAC. When the MRH-R receives this command, it performs initialization sequence on the MRH-R RAC. The initialization process includes executing the power-up sequence to the RAC, powering up the DRCG's for enabled 'stick' channels, and Current and Temperature Calibrating of the MRH-R 'expansion' channel RAC. |

|      | 010 = Manual Current Calibrate the RAC. When the MRH-R receives this command, it issues a Manual Current Calibrate sequence to ALL the RACs. The current control values specified in the EXCC, CACC, CBCC registers are used as the manual current control values.                                                                             |

|      | 011 = <b>Temperature Calibrate the RAC.</b> When the MRH-R receives this command, it issues a Temperature Calibrate sequence to ALL the RACs.                                                                                                                                                                                                  |

|      | 100 = <b>Set Fast Clock (SETF).</b> When the MRH-R receives this command, it issues a Set Fast clock sequence to the RAC.                                                                                                                                                                                                                      |

|      | 101 = Initialize Stick RACs. When the MRH-R receives this command, it performs initialization sequence on the MRH-R 'stick' channel RACs. The initialization process includes executing the power-up sequence to the RAC, and RAC Current and Temperature Calibration.                                                                         |

|      | 111 = Reserved                                                                                                                                                                                                                                                                                                                                 |

### 3.8. RACAL—Stick Channel A RAC Configuration Low WORD Register

Address: 10h

Default: 0000h

Access: Read / Write

Size: 16 bits

| Bit  | Description                                                          |

|------|----------------------------------------------------------------------|

| 15:0 | RAC Configuration Bits [15:0]. Bits [15:0] of the RAC configuration. |

### 3.9. RACAH—Stick Channel A RAC Configuration High WORD Register

Address: 11h

Default: 0000h

Access: Read / Write

Size: 16 bits

| Bit  | Description                                                            |

|------|------------------------------------------------------------------------|

| 15:0 | RAC Configuration Bits [31:16]. Bits [31:16] of the RAC configuration. |

### 3.10. RACBL—Stick Channel B RAC Configuration Low Word Register

Address: 12h

Default: 0000h

Access: Read / Write

Size: 16 bits

| Bit  | Description                                                          |

|------|----------------------------------------------------------------------|

| 15:0 | RAC Configuration Bits [15:0]. Bits [15:0] of the RAC configuration. |

### 3.11. RACBH—Stick Channel B RAC Configuration High Word Register

Address: 13h

Default: 0000h

Access: Read / Write

Size: 16 bits

|                                                                             | Bit | Description                                                            |

|-----------------------------------------------------------------------------|-----|------------------------------------------------------------------------|

| 15:0 RAC Configuration Bits [31:16]. Bits [31:16] of the RAC configuration. |     | RAC Configuration Bits [31:16]. Bits [31:16] of the RAC configuration. |

### 3.12. RACXL—Expansion Channel RAC Configuration Low Word Register

Address: 14h

Default: 0000h

Access: Read / Write

Size: 16 bits

| Bit  | Description                                                          |

|------|----------------------------------------------------------------------|

| 15:0 | RAC Configuration Bits [15:0]. Bits [15:0] of the RAC configuration. |

### 3.13. RACXH—Expansion Channel RAC Configuration High Word Register

Address: 15h

Default: 0000h

Access: Read / Write

Size: 16 bits

| Bit   | Description                         |  |  |  |

|-------|-------------------------------------|--|--|--|

| 15:12 | Reserved                            |  |  |  |

| 11:10 | On-die Termination Resistor Enable. |  |  |  |

|       | 00 = Disabled                       |  |  |  |

|       | 01 = Reserved                       |  |  |  |

|       | 10 = Reserved                       |  |  |  |

|       | 11 = Enabled                        |  |  |  |

| 9:0   | Reserved                            |  |  |  |

### 3.14. INIT—MRH-R Initialization Register

Address: 21h

Default: 009Fh

Access: R/W

Size: 16 bits

| Bit  | Descriptions                                                                                                                                                                                                  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15:8 | Reserved.                                                                                                                                                                                                     |  |

| 7    | SIO repeater bit (SRP). This bit controls the value on the MRH_SIO pin. After an SIO Reset command is executed, SRP will have a logic value of 1.                                                             |  |

|      | 1 = MRH_SIO = ExSIO                                                                                                                                                                                           |  |

|      | 0 = MRHSIO = 1                                                                                                                                                                                                |  |

| 6:5  | Reserved                                                                                                                                                                                                      |  |

| 4:0  | <b>Serial ID.</b> This field specifies the Serial ID of the MRH-R. The serial ID is compared against the serial address in initialization request packets to determine if this is the addressed MRH-R device. |  |

### 3.15. CNFGA—MRH-R Configuration Register

Address: 23h

Default: 8001h

Access: Read only

Size: 16 bits

| Bit Descriptions |                                                                                                                                                                                                      |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15               | MRH-R Identification. This field identifies the addressed device. When set to 1, the device is MRH-R. When set to 0, the addressed device is an RDRAM device. This field must be set to 1 for MRH-R. |  |

| 14:6             | Reserved                                                                                                                                                                                             |  |

| 5:0              | Manufacturer. This field specifies the manufacturer ID.                                                                                                                                              |  |

### 3.16. ST—Stepping Register

Address: 24h

Default: 0000h

Access: Read only

Size: 16 bits

| Bit                                                                                                     | Descriptions                                                    |  |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|

| 15:8                                                                                                    | Reserved                                                        |  |

| 7:4 <b>Protocol Revision.</b> This field specifies the version of the Direct RDRAM channel implemented. |                                                                 |  |

| 3:0                                                                                                     | Stepping. This field specifies the manufacturer version number. |  |

|                                                                                                         | 000 = A-1 Stepping                                              |  |

|                                                                                                         | 010 = A-2 Stepping                                              |  |

|                                                                                                         | All others = Reserved                                           |  |

### 4. Functional Description

### 4.1. MRH-R and the Direct RDRAM Channel

### 4.1.1. Operation Overview

The MRH-R acts as a Direct RDRAM channel expander by duplicating the signal activities on the 'expansion' channel to the specified 'stick' channel and vice versa. There is a time delay between the signal activities happening on the 'expansion' bus and the same signal activities on the 'stick' channels. This time delay must be constant under all operating conditions. The delay for RSL signals and delay for CMOS signals are different.

The MRH-R has the logic capability to help the MCH to maximize channel efficiency. This includes doing Refresh, Precharge After Refresh, Nap Exit, Power-down Exit, RAC Current Calibrate, RAC Current Calibrate & Sample, and Temperature Calibrate of devices on a channel upon request from the MCH.

The MRH-R contains registers for configuration and control. These registers are accessed through a three signal CMOS interface. The MRH-R implements a similar three signal CMOS interface for each 'stick' channel to reset and initialize RDRAMs. The same interface is used for accessing the internal registers of the RDRAM devices.

### 4.1.2. Signal and Protocol Overview

The 'Expansion' Channel (Ex) consists of the set of signals used to transmit information to and from the MRH-Rs and the protocol that defines the format and sequencing of this information. Both the signals and protocol of the 'expansion' channel are a superset of the their counterparts on the Direct RDRAM 'stick' channels. This allows efficient use of the multitude of 'stick' channels supported. Access can be pipelined with and across the Direct RDRAM channels, and sufficient control bandwidth is provided so that channel service operations such as refresh can proceed in parallel with fully pipelined memory accesses.

A Direct RDRAM Channel consists of two groups of high speed (RSL) control signals, a high speed (RSL) data bus, and a group of low speed CMOS control signals. The control signal groups are referred to as the Row Request Bus and the Column Request Bus. Each of these request busses has a request packet format associated with it—Row Request Packet (RRQP) and Column Request Packet (CRQP). Row and Column request packets can be pipelined to maximize data throughput to and from the memory.

To achieve full bandwidth operation on the 'expansion' channel, all control operations must be pipelined with the memory request packets. Further, independent expansion control must be allocated for the Row Request (RRq) and Column Request (CRq) packets on the 'stick' channels to maintain the variable RAS to CAS timings. This requirement results in two extra signals on the 'expansion' channel—Row Control Bus (EXP1), and Column Control Bus (EXP0).

Control packets on the 'expansion' channel are issued using EXP1 and EXP0 with the corresponding Row Request and Column Request packets. They are used to select the MRH-R that supports the targeted

'stick' channel. The EXP1 and EXP0 are used by the MRH-R to decode the Channel ID and route the incoming request packets appropriately. Because the underlying 'expansion' channel request packets have the same format as the 'stick' channel request packets, there is no command or address translation involved.

Expansion control packets provide support operations and the requisite control channel bandwidth for maintaining the many memory channels in a system. For example, the 'expansion' channel provides a channel refresh command that can be overlaid on memory access requests and that does not reduce memory bandwidth. In addition to refresh, the 'expansion' control packets provide commands for memory channel powerdown exit, nap exit, precharge after refresh, current control and temperature calibrate for 'expansion' bus. These, as well, have control channel bandwidth allocated so that memory accesses are not impacted.

### 4.1.2.1. Refresh and Post-Refresh Precharge

The 'expansion' channel architecture supports the issue of broadcast refresh and post-refresh precharge operations to a specified 'stick' channel that can be carried out concurrent with memory accesses. This allows the effective BW overhead of memory refresh to be reduced.

### 4.1.2.2. Power Mode Control

The 'expansion' channel provides a control mechanism that allows an entire channel to be NAP-exited as well as device-specific NAP exited.

The 'expansion' channel architecture also provides a control mechanism that allows a channel to be activated from the power-down state concurrent with memory accesses. This is useful when a system is being powered up. The first channel to be accessed will be powered up using an RDRAM request packet. The 'expansion' channel mechanism allows additional channels to be powered up concurrently with accesses to already powered channels.

Refer to Rambus\* Technical Documentation for detailed information.

#### 4.1.2.3. Current Calibration

The current calibration of an RDRAM device on a MRH-R 'stick' channel is performed by the MCH through a Secondary Control Packet (SCP) command. The MCH issues three consecutive Current Calibrate SCP commands followed by a Current Calibrate and Sample SCP command to the targeted RDRAM device.

The current calibration of the 'expansion' channel RAC and the 'stick' channel RACs in the MRH-R is accomplished through an EXP0 packet. The MCH issues three consecutive Expansion Current Calibrate commands followed by a Expansion Current Calibrate and Sample command to the targeted MRH-R.

On its 'expansion' channel interface (slave RAC), the MRH-R drives the ExDQB[4:3] pins to perform the current calibration function. On the Direct RDRAM 'stick' channel A and 'stick' channel B (master RACs), the MRH-R performs current calibration on the CHx\_DQB[2:1] pins. This allows the MCH to perform current calibration at the same time as the MRH-Rs on the 'expansion' channel. Note also that an MRH-R can perform current calibration on it's own RACs at the same time as an RDRAM on it's own 'stick' channels since they use different DQ pins.

### 4.1.2.4. Thermal Sensor Read