## Intel® 82806AA PCI 64 Hub (P64H)

**Datasheet**

**November 1999**

Order Number: 298025-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 82806AA PCI 64 Hub (P64H) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

$l^2C$  is a 2-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $l^2C$  bus/protocol and was developed by Intel. Implementations of the  $l^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Alert on LAN is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation www.intel.com or call 1-800-548-4725

\*Third-party brands and names are the property of their respective owners.

Copyright © Intel Corporation 1999

# intel.

# Contents

| 1. | Signa | al Description                                                            | 11   |

|----|-------|---------------------------------------------------------------------------|------|

|    | 1.1.  | Hub Interface to the Host Controller                                      | 11   |

|    | 1.2.  | PCI Interface                                                             |      |

|    | 1.3.  | Interrupt Interface                                                       |      |

|    |       | Clocks                                                                    |      |

|    | 1.4.  |                                                                           |      |

|    | 1.5.  | Miscellaneous                                                             |      |

|    | 1.6.  | Power and Ground Signals                                                  | 15   |

| 2. | Regis | ster Description                                                          | 17   |

|    | 2.1.  | Register Nomenclature and Access Attributes                               | 17   |

|    | 2.2.  | Hub Interface to PCI Bridge Registers (D31:F0)                            | 18   |

|    |       | 2.2.1. VID—Vendor ID Register (D31:F0)                                    |      |

|    |       | 2.2.2. DID—Device ID (D31:F0)                                             |      |

|    |       | 2.2.3. CMD—Device Command (D31:F0)                                        |      |

|    |       | 2.2.4. PD_STS—Primary Device Status Register (D31:F0)                     | 21   |

|    |       | 2.2.5. REVID—Revision ID (D31:F0)                                         |      |

|    |       | 2.2.6. PIF – Programming Interface                                        | 22   |

|    |       | 2.2.7. SCC—Sub-Class Code Register (D31:F0)                               |      |

|    |       | 2.2.8. BCC—Base-Class Code Register (D31:F0)                              |      |

|    |       | 2.2.9. CLS—Cache Line Size Register (D31:F0)                              |      |

|    |       | 2.2.10. PMLT—Primary Master Latency Timer (D31:F0)                        |      |

|    |       | 2.2.11. HEADTYP—Header Type Register (D31:F0)                             |      |

|    |       | 2.2.12. PBUS_NUM—Primary Bus Number Register (D31:F0)                     |      |

|    |       | 2.2.13. SBUS_NUM—Secondary Bus Number Register (D31:F0)                   |      |

|    |       | 2.2.14. SUB_BUS_NUM—Subordinate Bus Number Register (D31:F0)              |      |

|    |       | 2.2.15. SMLT—Secondary Master Latency Timer (D31:F0)                      |      |

|    |       | 2.2.16. IOBASE—I/O Base Register (D31:F0)                                 |      |

|    |       | 2.2.17. IOLIM—I/O Limit Register (D31:F0)                                 | ∠5   |

|    |       | 2.2.18. SECSTS—Secondary Status Register (D31:F0)                         |      |

|    |       | 2.2.20. MEMLIM—Non-Prefetchable Memory Limit Address Register (D31:F0)    |      |

|    |       | 2.2.21. PREF_MEM_BASE—Prefetchable Memory Base Address Register (D31:1 0) |      |

|    |       | 2.2.22. PREF MEM LIM—Prefetchable Memory Limit Address Register (D31:F0)  |      |

|    |       | 2.2.23. PREF_MEM_BASE_UPPER—Prefetchable Memory Base Upper 32-Bit         | , 20 |

|    |       | Address Register (D31:F0)                                                 | 29   |

|    |       | 2.2.24. PREF_MEM_LIM_UPPER—Prefetchable Memory Base Upper 32-Bit Add      |      |

|    |       | Register (D31:F0)                                                         |      |

|    |       | 2.2.25. IOBASE_HI—I/O Base Upper 16-Bit Address Register (D31:F0)         | 29   |

|    |       | 2.2.26. IOBASE_LO—I/O Limit Upper 16-Bit Address Register (D31:F0)        | 30   |

|    |       | 2.2.27. INT_LINE—Interrupt Line Register (D31:F0)                         | 30   |

|    |       | 2.2.28. BRIDGE_CNT—Bridge Control Register (D31:F0)                       | 30   |

|    |       | 2.2.29. CNF—P64H Configuration Register (D31:F0)                          | 32   |

|    |       | 2.2.30. Multi-Transaction Timer (MTT) Register (D31:F0)                   |      |

|    |       | 2.2.31. Soft_DT_Timer—Soft Delayed Transaction Timer Register (D31:F0)    |      |

|    |       | 2.2.32. ERR_CMD—Error Command Register (D31:F0)                           |      |

|    |       | 2.2.33. ERR_STS—Error Status Register (D31:F0)                            |      |

|    | 2.3.  | Advanced Interrupt Controller (APIC) Registers (D0:F0)                    |      |

|    |       | 2.3.1. VID—Vendor ID Register (D0:F0)                                     | 35   |

|    |       | 2.3.2. DID—Device ID Register (D0:F0)                                     |      |

|    |       | 2.3.3. CMD—Command Register (D0:F0)                                       | 36   |

|    |       | 2.3.4.           | STS—Device Status Register (D0:F0)                                    | 37 |

|----|-------|------------------|-----------------------------------------------------------------------|----|

|    |       |                  | REVID—Revision ID (D0:F0)                                             |    |

|    |       | 2.3.6.           | PIF—Programming Interface Register (D0:F0)                            | 37 |

|    |       | 2.3.7.           | SCC—Sub-Class Code Register (D0:F0)                                   | 37 |

|    |       | 2.3.8.           | BCC—Base-Class Code Register (D0:F0)                                  |    |

|    |       | 2.3.9.           | HEADTYP—Header Type Register (D0:F0)                                  |    |

|    |       |                  | . BAR—IOAPIC Memory Base Address Register (D0:F0)                     |    |

|    |       |                  | SUB_VID—Subsystem Vendor ID Register (D0:F0)                          |    |

|    |       | 2.3.12           | SUB_ID—Subsystem ID Register (D0:F0)                                  | 39 |

|    |       | 2.3.13           | . APIC_BASE—I/O APIC Base Register (D0:F0)                            | 39 |

|    | 2.4.  |                  | C Registers                                                           |    |

|    | 2     | 2.4.1.           | Index Register (D0:F0)                                                |    |

|    |       | 2.4.2.           | Window Register (D0:F0)                                               |    |

|    |       | 2.4.2.           | IRQ Pin Assertion Register (D0:F0)                                    | 41 |

|    |       | 2.4.3.<br>2.4.4. | EOI Register (D0:F0)                                                  |    |

|    |       | 2.4.4.           |                                                                       |    |

|    |       |                  | ID Register (D0:F0)                                                   |    |

|    |       | 2.4.6.           | Version Register (D0:F0)                                              |    |

|    |       | 2.4.7.           | ARBID—Arbitration ID Register (D0:F0)                                 |    |

|    |       | 2.4.8.           | Redirection Table Low DWord (D0:F0)                                   |    |

|    |       | 2.4.9.           | Redirection Table High DWord                                          | 46 |

| 3. | Funct | ional Des        | scription                                                             | 47 |

|    | 3.1.  |                  | ss Decoding                                                           |    |

|    | 3.1.  |                  |                                                                       |    |

|    |       | 3.1.1.           | I/O Address Decoding                                                  |    |

|    |       |                  | 3.1.1.1. I/O Base/Limit Address Registers                             |    |

|    |       | 3.1.2.           |                                                                       |    |

|    |       |                  | 3.1.2.1. Non-Prefetchable Memory Base/Limit Address Registers         |    |

|    |       |                  | 3.1.2.2. Prefetchable Memory Base/Limit Address Registers             |    |

|    |       |                  | 3.1.2.3. P64H 44-Bit Addressing                                       |    |

|    |       | 3.1.3.           | VGA Mode                                                              |    |

|    |       |                  | 3.1.3.1. Memory Map                                                   |    |

|    |       |                  | PCI Devices and Functions                                             |    |

|    | 3.2.  | PCI Bu           | us Operation                                                          |    |

|    |       | 3.2.1.           | Types of Transactions                                                 | 52 |

|    |       | 3.2.2.           | Address Phase                                                         | 53 |

|    |       | 3.2.3.           | Write Transactions                                                    | 54 |

|    |       | 3.2.4.           | Read Transactions                                                     | 55 |

|    |       | 3.2.5.           | Configuration Transaction                                             |    |

|    |       | 3.2.6.           | 64-Bit Operation                                                      | 59 |

|    |       |                  | Transaction Termination                                               |    |

|    |       |                  | 3.2.7.1. Master Termination Initiated by the P64H                     |    |

|    |       |                  | 3.2.7.2. Master Abort Received by the P64H                            |    |

|    |       |                  | 3.2.7.3. Target Termination Received by the P64H                      |    |

|    | 3.3.  | Transa           | action Ordering                                                       |    |

|    | 0.0.  | 3.3.1.           | Transactions Governed by Ordering Rules                               |    |

|    |       | 3.3.2.           | General Ordering Guidelines                                           |    |

|    |       | 3.3.3.           | Ordering Rules                                                        |    |

|    | 2.4   |                  |                                                                       |    |

|    | 3.4.  |                  | Handling                                                              |    |

|    |       | 3.4.1.           | P64H Error Reporting Model                                            |    |

|    |       | 3.4.2.           | Address Parity Errors                                                 |    |

|    |       | 3.4.3.           | Data Parity Errors                                                    |    |

|    |       |                  | 3.4.3.1. Configuration Write Transactions to P64H Configuration Space |    |

|    |       |                  | 3.4.3.2. Read Transactions (Data Parity)                              |    |

|    |       |                  | 3.4.3.3. Posted Write Transactions (Data Parity)                      | 69 |

## int<sub>e</sub>l.

|    |       | 3.4.3.4. I/O Write Transaction                                 | 69 |

|----|-------|----------------------------------------------------------------|----|

|    |       | 3.4.4. Master Aborts                                           |    |

|    |       | 3.4.4.1. Non-Posted Transactions                               |    |

|    |       | 3.4.4.2. Posted Write Transactions                             |    |

|    |       | 3.4.4.3. Exclusive Access Master-Abort                         |    |

|    |       | 3.4.5. System Error (SERR#) Reporting                          |    |

|    |       | 3.4.5.1. PCI SERR# Pin Assertion                               |    |

|    |       | 3.4.5.2. Other System Error                                    |    |

|    | 3.5.  | Advanced Interrupt Controller (APIC)                           |    |

|    |       | 3.5.1. Interrupt Handling                                      |    |

|    |       | 3.5.2. Interrupt Mapping                                       |    |

|    |       | 3.5.3. APIC Bus Functional Description                         |    |

|    |       | 3.5.3.1. Physical Characteristics of APIC                      |    |

|    |       | 3.5.3.2. APIC Bus Arbitration                                  |    |

|    |       | 3.5.3.3. Bus Message Formats                                   |    |

|    |       | 3.5.3.3.1. EOI Message For Level Triggered Interrupts          | 74 |

|    |       | 3.5.3.3.3. Lowest Priority Message Without Focus Processor (FP |    |

|    |       | 3.5.3.3.4. Remote Read Message                                 |    |

|    |       | 3.5.4. Boot Interrupt                                          |    |

|    | 3.6.  | Clocking and Reset                                             |    |

|    | 0.0.  | 3.6.1. Clocking                                                |    |

|    |       | 3.6.2. Reset                                                   |    |

|    |       | 3.6.2.1. Reset In (RSTIN#)                                     |    |

|    |       | 3.6.2.2. Secondary Bus Reset                                   |    |

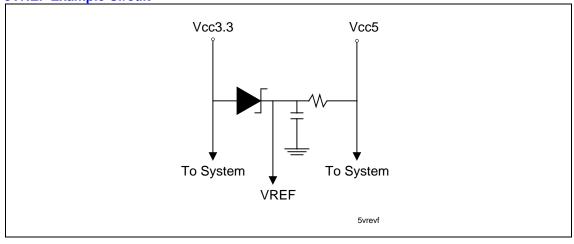

|    | 3.7.  | Reference Power Voltage                                        |    |

|    |       | 3.7.1. 5V Reference Requirements                               |    |

| 1. | Pinou | and Package Information                                        | 83 |

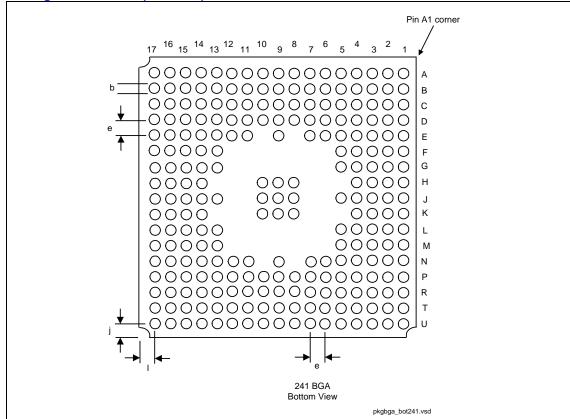

|    | 4.1.  | P64H Pin Assignment                                            |    |

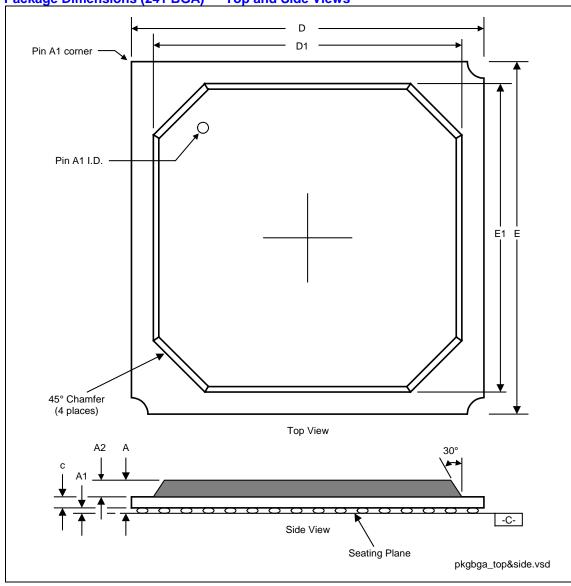

|    | 4.2.  | Package Specificaiton                                          |    |

|    | 4.2.  | Package Specification                                          | 00 |

| 5. | Testa | pility                                                         | 91 |

|    | 5.1.  | Tri-state Mode                                                 | 91 |

|    | 5.2.  | NAND Tree Mode                                                 | 91 |

|    |       |                                                                |    |

## **Figures**

| Figure 1. P64H System Interface                             |    |

|-------------------------------------------------------------|----|

| Figure 2. Configuration Transaction Address Format          |    |

| Figure 3. Type 1 to Type 0 Transaction                      | 57 |

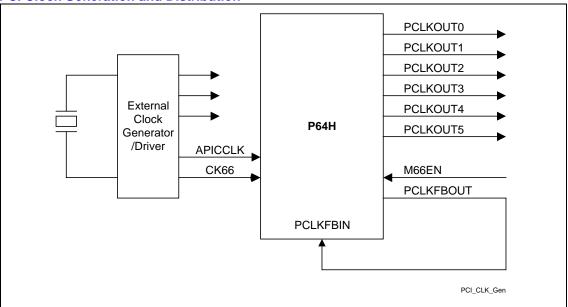

| Figure 4. PCI Clock Generation and Distribution             |    |

| Figure 5. 5VREF Example Circuit                             | 81 |

| Figure 6. P64H Ballout (Top View, Left Side)                | 84 |

| Figure 7. P64H Ballout (Top View, Right Side)               | 85 |

| Figure 8. Package Dimensions (241 BGA) — Top and Side Views |    |

| Figure 9. Package Dimensions (241 BGA) — Bottom View        |    |

## **Tables**

| Table 1. Hub Interface Signals                            | 11 |

|-----------------------------------------------------------|----|

| Table 2. PCI Interface Signals                            | 12 |

| Table 3. Interrupt Interface Signals                      | 14 |

| Table 4. Clock Signals                                    |    |

| Table 5. Miscellaneous Signals                            | 15 |

| Table 6. Power and Ground Signals                         |    |

| Table 7. PCI Configuration Map (Hub Interface-PCI—D30:F0) | 18 |

| Table 8. APIC Configuration Registers (D0:F0)             | 35 |

| Table 9: APIC Direct Registers                            | 40 |

| Table 10: APIC Direct Access Memory Registers             | 40 |

| Table 11. Indirect Access Memory Register                 | 42 |

| Table 12. PCI Devices and Functions                       | 51 |

| Table 13. P64H PCI Transaction                            | 52 |

| Table 14. Posted Write Forwarding                         | 54 |

| Table 15. Termination Transaction by the Initiator        | 61 |

| Table 16. Termination Transaction by the Target           | 61 |

| Table 17. Transaction Ordering Rules                      | 64 |

| Table 18. Ordering Relation Per Transaction               | 66 |

| Table 19. Arbitration Cycles                              | 73 |

| Table 20. APIC Message Formats                            | 73 |

| Table 21. EOI Message                                     | 74 |

| Table 22. Short Message                                   | 75 |

| Table 23: APIC Bus Status Cycle Definition                | 76 |

| Table 24. Lowest Priority Message Without Focus Processor | 77 |

| Table 25. Remote Read Message                             | 78 |

| Table 26. P64H Alphabetical Ballout Assignment            | 86 |

| Table 27. BGA Package Dimensions (241 BGA)                | 89 |

| Table 28. NAND Tree Chains                                | 92 |

|                                                           |    |

## **Revision History**

|    | Rev. | Draft/Changes            | Date |

|----|------|--------------------------|------|

| -( | -001 | Initial Release     Nove |      |

## Intel® 82806AA PCI 64 Hub (P64H)

#### **Product Features**

- PCI Interface

- Supports both 64bit/32bit 33 MHz or 66 MHz devices

- Provides Synchronous operation to hub interface bus using 1:1(66 MHz) or 2:1(33MHz) hub interface/ PCI Bus gearing ratio

- Allows I/O transactions to occur concurrently with processor transactions to isolate traffic

- Supports Parity and System Error (PERR#/ SERR#)

- Allows peer-to-peer communication within a single PCI bus segment

- Provides PCI transaction forwarding for all I/O and memory

- —Provides address decoding for:

- 16-bit I/O addressing

- 32-bit non-prefetchable memory addressing

- 44-bit prefetchable memory addressing (upstream only)

- VGA addressing

- Includes downstream LOCK# capabilities

- Supports Fast Back-to-Back cycles (upstream only)

- -Supports bus parking

- Implements Delayed Transaction for:

- PCI configuration read/write,

- I/O read, and memory read commands (downstream);

- Memory read, I/O read and I/O write commands (upstream)

- Scalability/ Flexibility

- Provides arbitration support for 6 PCI devices

- Supports either 2 x 66 MHz or 4 x 33 MHz PCI slots

- Processes dual address cycle (DAC) for upstream access >4GB

- Handles 3.3V operation with 5.0V tolerant on all input pins

- Upstream Hub Interface

- Connects to the MCH via a 16-bit hub interface

- Provides 64-bit and 32-bit addressing

- Utilizes 66 MHz base clock

- Integrated Functions

- I/OAPIC to provide 24 interrupts

- Six copies of PCLKOUT signals to its PCI devices

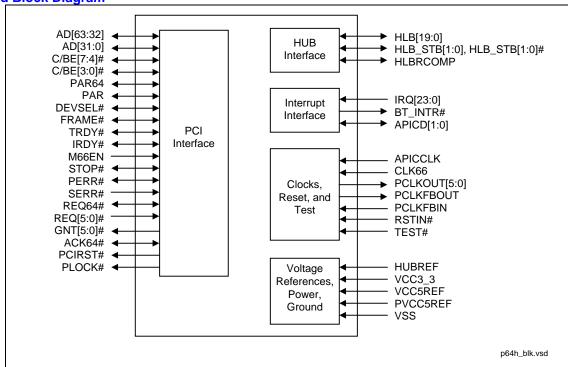

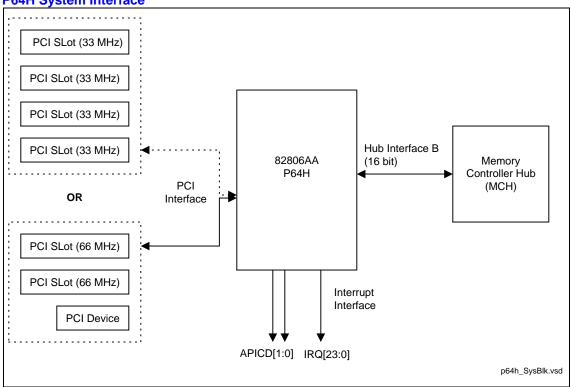

The Intel<sup>®</sup> 82806AA PCI-64 Hub (P64H) is a multi-function PCI device that provides a PCI bridging function and an I/O Advanced Peripheral Interrupt Controller (APIC) function. The P64H is an integral part of the Intel<sup>®</sup> 840 chipset and future chipsets.

The P64H performs PCI bridging functions between the hub interface and the PCI Bus. The P64H has a 16-bit primary hub interface to the Memory Controller Hub (MCH) and a secondary 64-bit PCI Bus interface. This controller operates transparently with either 64-bit or 32-bit devices and supports either two 66 MHz or four 33 MHz PCI slots. The P64H also integrates I/O APIC controller functions. The interrupt controller provides up to 24 interrupts. In addition, the P64H provides 6 copies of the PCI clock

The Intel® 82806AA P64H product may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

**Simplified Block Diagram**

Figure 1. P64H System Interface

int<sub>el</sub>.

## 1. Signal Description

This section provides a detailed description of P64H signals. The signals are arranged in functional groups according to their associated interface. The states of all of the signals during reset are provided in the System Reset section.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name the signal is asserted when at the high voltage level.

The following notations are used to describe the signal type:

I Input pin

O Output pin

**OD** Open Drain Output pin.

**I/OD** Input / Open Drain Output pin.

I/O Bi-directional Input/Output pin

#### 1.1. Hub Interface to the Host Controller

**Table 1. Hub Interface Signals**

| interrace digitals |             |                                                                                                                                                                                                                  |  |

|--------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name               | Туре        | Description                                                                                                                                                                                                      |  |

| HLB_STB[1:0]       | I/O<br>CMOS | Hub Interface Packet Strobe: This signal is a part of the differential strobe pair. This signal is used to transmit or receive the data on the hub interface.                                                    |  |

| HLB_STB[1:0]#      | I/O<br>CMOS | <b>Hub Interface Packet Strobe Complement</b> : This signal is a part of the differential strobe pair. This signal is used to transmit or receive the data on the hub interface.                                 |  |

| HLBRCOMP           | I/O<br>CMOS | Hub Interface B Resistive Compensation: This signal is used to calibrate the hub interface B I/O buffers. The P64H only supports RCOMP. This signal must be tied to ground via a 30 $\Omega$ pull-down resistor. |  |

| HLB[19:0]          | I/O<br>CMOS | Hub Interface Signals:                                                                                                                                                                                           |  |

### 1.2. PCI Interface

**Table 2. PCI Interface Signals**

| CI Interface Signals |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name                 | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| AD[63:32]            | I/O  | PCI Address/Data: AD[63:32] signals are multiplexed address and data bus. This provides an additional 32 bits to the PCI bus. During the address phase (when dual address command is used and REQ64# is asserted), the upper 32 bits are transferred. During the data phase, an additional 32 bit of data are transferred when REQ64# and ACK64# are both asserted. Unused AD[63:32] signals should be pulled up, to a valid logic level, through external resistors.                                                                                                                                                                                                                              |  |  |  |

| AD[31:0]             | I/O  | <b>PCI Address/Data:</b> AD[31:0] signals are multiplexed address and data bus. During the first clock of a transaction, AD[31:0] contains a physical byte address (32 bits). During the subsequent clocks, AD[31:0] contain data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| C/BE[7:4]#           | I/O  | Bus Command and Byte Enables Upper 4 bits: C/BE[7:4]# signals are multiplexed command field and byte enable field. During the address phase (when the dual address command is used and REQ64# is asserted), the initiator will drive the transaction type on C/BE[7:4]#. Otherwise, these bits are undefined and the initiator drives a valid logic level onto the pins. During the data phase, the initiator will drive byte enables for the AD[63:32] data bits when REQ64# and ACK64# are both asserted. Unused C/BE[7:4]# signals should be pulled up, to a valid logic level, through external resistors.                                                                                     |  |  |  |

| C/BE[3:0]#           | I/O  | <b>Bus Command and Byte Enables:</b> These signals are a multiplexed command field and byte enable field. During the address phase of a transaction, C/BE[3:0]# define the bus command. During the data phase, C/BE[3:0]# define the byte enables.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                      |      | C/BE[3:0]# Command Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                      |      | 0001 Special Cycle 0010 I/O Read 0011 I/O Write 0110 Memory Read 0111 Memory Write 1010 Configuration Read 1011 Configuration Write 1100 Memory Read Multiple 1101 Dual Address Cycle 1110 Memory Read Line 1111 Memory Write and Invalidate                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                      |      | All command encoding not shown are reserved. The P64H will not decode reserved values, and will not respond if a PCI master generates a cycle using one of the reserved values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      |      | NOTE: The Memory Read Multiple and Memory Read Line will be sent by the P64H on the hub interface as a Memory Reads. The Memory write and invalidate will be sent by P64H on the hub interface as Memory Writes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| PAR64                | I/O  | Upper 32-bits Parity: Signal PAR64 carries the even parity of AD[63:32] and C/BE[7:4]# for both address and data phases. Signal PAR64 is driven by the initiator and is valid one clock cycle after the first address phase when a dual address command is indicated by C/BE[3:0]# and REQ64# is asserted. Signal PAR64 is also valid one clock cycle after the second address phase of a dual address transaction when REQ64# is asserted. Once PAR64 is valid, it remains valid for one clock after the completion of the data phase. PAR64 share the same timing as AD[63:32] but delayed by one clock. If unused, PAR64 should be pulled up to a valid logic level through external resistors. |  |  |  |

| Name      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAR       | I/O  | Parity: PAR is "even" parity and is calculated on 36 bits - AD[31:0] plus C/BE[3:0]#. "Even" parity means that the sum of 1's, within the 36 bits plus PAR, is always even. PAR is always calculated on 36 bits regardless of the valid byte enables. PAR is generated for address and data phases, and is only guaranteed to be valid one PCI clock after the corresponding address or data phase. PAR is driven and tri-stated identically to the AD[31:0] lines but PAR is delayed by one PCI clock. PAR is an output during the P64H address phase (delayed one clock) and data phase. The P64H checks parity when it is the initiator of read transaction and when it is the target of write transactions. |

| DEVSEL#   | I/O  | Device Select: The P64H asserts DEVSEL# to claim a PCI transaction. As an output (P64H Target), the P64H asserts DEVSEL# when a PCI master peripheral attempts an access to an internal P64H address or an address destined for hub interface (main memory or AGP). As an input (P64H Initiator), DEVSEL# indicates the response to a P64H-initiated transaction on the PCI bus. For P64H initiated transaction, it looks for the assertion of DEVSEL# within five cycles of FRAME# assertion; otherwise the P64H terminates the transaction with a master abort. DEVSEL# is tri-stated from the leading edge of PCIRST#. DEVSEL# remains tri-stated by the P64H until driven as a target.                      |

| FRAME#    | I/O  | <b>Frame:</b> The initiator drives FRAME# to indicate the beginning and duration of an access. Data transfers continues as long as FRAME# is asserted. When FRAME# is deasserted, this indicates the final data phase. FRAME# is an input when the P64H is the Target. FRAME# is an output when the P64H is the initiator. FRAME# remains tri-stated by the P64H until driven as an initiator.                                                                                                                                                                                                                                                                                                                  |

| IRDY#     | I/O  | Initiator Ready: IRDY# indicates the P64H's ability, as an Initiator, to complete the current data phase of the transaction. It is used in conjunction with TRDY#. A data phase is completed on any clock when both IRDY# and TRDY# are sampled asserted. During a write, IRDY# indicates the P64H has valid data present on AD[31:0]. During a read, it indicates the P64H is prepared to latch data. IRDY# is an input to the P64H when the P64H is the Target and an output when the P64H is an Initiator. IRDY# remains tristated by the P64H until driven as an initiator.                                                                                                                                 |

| TRDY#     | I/O  | Target Ready: TRDY# indicates the P64H's ability to complete the current data phase of the transaction. TRDY# is used in conjunction with IRDY#. A data phase is completed when both TRDY# and IRDY# are sampled asserted. During a read, TRDY# indicates that the P64H (target) has placed valid data on its AD lines. During a write, it indicates that the P64H (target) is prepared to latch data. TRDY# is an input to the P64H when it is the initiator and an output when it is a target. TRDY# is tri-stated from the leading edge of PCIRST#. TRDY# remains tri-stated by the P64H until driven as a target.                                                                                           |

| M66EN     | I    | <b>66 MHz Enable:</b> This signal indicates the speed of the PCI Bus. If it is high then the Bus speed is 66 MHz and if it is low then the bus speed is 33 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| STOP#     | I/O  | Stop: STOP# indicates that the P64H (target) is requesting the initiator to stop the current transaction. As an initiator, STOP# causes the P64H to stop the current transaction. STOP# is an output when the P64H is a Target and an input when the P64H is an Initiator. STOP# is tri-stated from the leading edge of PCIRST# and remains tri-stated until driven by P64H.                                                                                                                                                                                                                                                                                                                                    |

| PERR#     | I/O  | Parity Error: The P64H drives PERR# when it detects a parity error during read/write transactions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SERR#     | I    | System Error: SERR# can be pulsed active by any PCI device that detects a system error condition. The P64H samples SERR# as an input and conditionally forwards it to the hub interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| REQ64#    | I/O  | PCI Request, 64-bit Transfer: This signal indicates that the initiator is requesting a 64-bit data transfer. REQ64# has the same timing as FRAME#. When the P64H is the initiator, this signal is an output. When the P64H is the target, this signal is an input.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| REQ[5:0]# | I    | <b>PCI Requests:</b> Supports up to 6 masters on the PCI bus. The P64H accepts six request inputs into its internal bus arbiter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Name      | Туре | Description                                                                                                                                                                                                                                                                                         |  |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GNT[5:0]# | 0    | PCI Grants: Supports up to six masters on the PCI bus. The arbiter can assert one of the six bus grant outputs, to indicate that an initiator can start a transaction on the PCI Bus.                                                                                                               |  |

| ACK64#    | I/O  | Acknowledge, 64-bit transfer: Signal ACK64# is asserted by target only when REQ64# is asserted by the initiator, to indicate the target's ability to transfer data using 64 bits. ACK64# has the same timing as DEVSEL#.                                                                            |  |

| PCIRST#   | 0    | PCI Reset: P64H asserts PCIRST# to reset devices that reside on its PCI bus. PCIRST# occurs when either RSTIN# is asserted or PCI reset bit (BRIDGE_CNT register) is set.                                                                                                                           |  |

| PLOCK#    | 0    | PCI Lock: Indicates exclusive bus operation and may require multiple transactions to complete. P64H asserts PLOCK# when it performs exclusive transactions on PCI. PLOCK# is ignored when PCI masters are granted the bus. The P64H does not propagate locked transaction upstream (hub interface). |  |

## 1.3. Interrupt Interface

**Table 3. Interrupt Interface Signals**

| Name       | Туре | Description                                                                                                                                                                                                                                                                                                        |

|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ[23:0]  | I    | Interrupt Request [23:0]: These are APIC interrupts and do not support (8259) PIC mode. External 8.2K pull-up resistors are required if these signals are not used.                                                                                                                                                |

| BT_INTR#   | O/OD | <b>Boot Interrupt:</b> This open drain signal should be tied to a ICH PIRQx to support boot devices on the P64H PCI segment. Upon power reset, P64H will forward the interrupt request to the ICH via this signal. This pin will automatically be disabled after the IOAPIC ID register is written by the OS.      |

| APICD[1:0] | I/OD | APIC Data: These bi-directional open drain signals are used to send and receive data over the APIC bus. As inputs the data is valid on the rising edge of APICCLK. As outputs, new data is driven from the rising edge of the APICCLK. External 8.2K pull-up resistors are required if these signals are not used. |

#### 1.4. Clocks

**Table 4. Clock Signals**

| Name         | Туре | Description                                                                                                                                                                                                                                   |  |

|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| APICCLK      | I    | APIC Clock: This clock is 16.66667 MHz and is the APIC bus clock. The clock frequency can be raised, up to 33 MHz, to support FRC mode on dual processor systems. External 8.2K pull-up resistors are required if these signals are not used. |  |

| CLK66        | I    | 66 MHz Clock: Used to run the hub interface.                                                                                                                                                                                                  |  |

| PCLKOUT[5:0] | 0    | <b>PCI Clock:</b> 33/66 MHz clock. PCICLK provides timing for all transactions on the PCI bus. These pins can be disabled via the P64H Configuration register. The default state is enabled.                                                  |  |

| PCLKFBOUT    | 0    | PCI Feedback Clock Out: This signal synchronizes the PCI clocks to the internal PLL. This signal should be fed into the P64H PCLKFBIN pin                                                                                                     |  |

| PCLKFBIN     | I    | PCI Feedback Clock In: This signal is used by the PLL to synchronize the PCI clock driven from PCLKFBOUT to the clock used for the internal PCI logic.                                                                                        |  |

#### 1.5. Miscellaneous

**Table 5. Miscellaneous Signals**

| Name      | Туре | Description                                                                                                                                                        |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSTIN#    | I    | Reset In: When asserted this signal will asynchronously reset the P64H logic.                                                                                      |

| TEST#     | I    | <b>Test:</b> This pin is used for manufacturing testing only. This signal contains an internal pull-up resistor. Externally, this pin must be pulled-up to Vcc3.3. |

| RSV[15:1] | I/O  | Reserved:_RSV1 and RSV3 must be pull-down to GND. Other RSV signals should not be used and left as N/C.                                                            |

## 1.6. Power and Ground Signals

**Table 6. Power and Ground Signals**

| Name     | Туре | Description                                                                                                                                                                                                                                   |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HUBREF   | I    | Hub interface Reference: Reference voltage input for the hub interface. This will be turned-off in power management states.                                                                                                                   |

| VCC3_3   | I    | 3.3V Core Voltage: This will be turned-off in power management states.                                                                                                                                                                        |

| VCC5REF  | I    | Vcc 5V Reference Voltage: The VCC5REF is the reference voltage for the IRQ signals. This will be turned-off in power management states. VCC5REF at ball P7 is used for RSTIN#. VCC5REF at ball H17 is used for the IRQ's, TEST#, and BT_INT#. |

| PVCC5REF | I    | PCI Vcc 5V Reference Voltage: The PVCC5REF is the reference voltage for PCI signals (excluding PCICLK signals).                                                                                                                               |

| VSS      | I    | Ground: Grounds for periphery and hub interface.                                                                                                                                                                                              |

Intel® 82806AA PCI 64 Hub (P64H)

int<sub>el</sub>.

## 2. Register Description

The P64H contains two PCI Devices—Hub Interface-to-PCI Bridge (Device 31 : Function 0) and an I/O APIC device (Device 0 : Function 0). This chapter describes these P64H configuration registers. A detailed bit description is provided.

- **Hub Interface-to-PCI Bridge (D31:F0).** This portion of the P64H implements the buffering and control logic between PCI and the hub interface. The PCI bus arbitration is handled by this PCI device. The PCI decoder in this device must decode the ranges for hub interface to the MCH. All register contents are lost when core well power is removed.

- **APIC device (D0:F0).** The P64H implements a variation of the APIC known as the IOAPIC. The IOAPIC reside on the secondary PCI bus (bus #1).

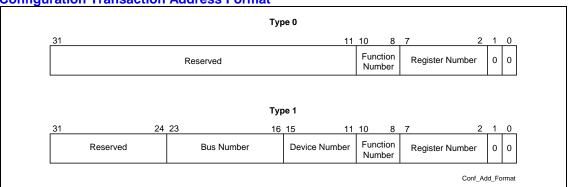

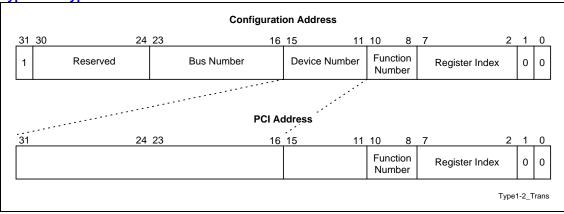

The P64H supports PCI configuration space accesses using the mechanism denoted as Configuration Mechanism #1 in the PCI specification.

#### 2.1. Register Nomenclature and Access Attributes

| Symbol                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RO                             | Read Only. If a register is read only, writes to this register have no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| WO                             | Write Only. If a register is write only, reads of this register return undefined results                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| R/W                            | Read/Write. A register with this attribute can be read and written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| R/WC                           | Read/Write Clear. A register bit with this attribute can be read and written. However, a write of a 1 clears (sets to 0) the corresponding bit and a write of a 0 has no effect.                                                                                                                                                                                                                                                                                                                                                                     |

| R/WO                           | Read/Write Once. A register bit with this attribute can be written to only once after power up. After the first write, the bit becomes read only.                                                                                                                                                                                                                                                                                                                                                                                                    |

| Reserved<br>Bits               | Software must deal correctly with fields that are reserved. On reads, software must use appropriate masks to extract the defined bits and not rely on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit positions are preserved. That is, the values of reserved bit positions must first be read, merged with the new values for other bit positions and then written back. Note the software does not need to perform read, merge, write operation for the configuration address register. |

| Reserved<br>Registers          | In addition to reserved bits within a register, the P64H contains address locations in its configuration space that are marked "Reserved. When a "Reserved" register location is read, a random value can be returned. ("Reserved" registers can be 8-, 16-, or 32-bit in size). Registers that are marked as "Reserved" must not be modified by system software. Writes to "Reserved" registers may cause system failure.                                                                                                                           |

| Default<br>Value Upon<br>Reset | Upon a Full Reset, the P64H sets all of its internal configuration registers to predetermined <b>default</b> states.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## 2.2. Hub Interface to PCI Bridge Registers (D31:F0)

The hub interface to PCI Bridge resides in PCI Device 31, Function 0 on the PCI bus.

Note: Reserved registers are read only and are not shown. Reads to these registers return all 0s.

Table 7. PCI Configuration Map (Hub Interface-PCI—D30:F0)

| Address<br>Offset | Mnemonic               | Register Name                                     | Default                               | Туре |

|-------------------|------------------------|---------------------------------------------------|---------------------------------------|------|

| 00–01             | VID                    | Vendor ID                                         | 8086h                                 | RO   |

| 02–03             | DID                    | Device ID                                         | 1360h                                 | RO   |

| 04–05             | CMD                    | Device Command Register                           | 0000h                                 | R/W  |

| 06–07             | PD_STS                 | Device Status Register                            | 00A0h                                 | R/WC |

| 08                | REVID                  | Revision ID                                       | See latest<br>Specification<br>Update | RO   |

| 09                | PIF                    | Programming Interface                             | 00h                                   | RO   |

| 0A                | SCC                    | Sub Class Code                                    | 04h                                   | RO   |

| 0B                | BCC                    | Base Class Code                                   | 06h                                   | RO   |

| 0C                | CLS                    | Cache Line Size Register                          | 00h                                   | RO   |

| 0D                | PMLT                   | Master Latency Timer                              | 00h                                   | RO   |

| 0E                | HEADTYP                | Header Type                                       | 80h                                   | RO   |

| 18                | PBUS_NUM               | Primary Bus Number                                | 00h                                   | R/W  |

| 19                | SBUS_NUM               | Secondary Bus Number                              | 00h                                   | R/W  |

| 1A                | SUB_BUS_NUM            | Subordinate Bus Number                            | 00h                                   | R/W  |

| 1B                | SMLT                   | Secondary Master Latency Timer                    | 00h                                   | R/W  |

| 1C                | IOBASE                 | IO Base Address Register                          | 00h                                   | R/W  |

| 1D                | IOLIM                  | IO Limit Address Register                         | 00h                                   | R/W  |

| 1E–1F             | SECSTS                 | Secondary Status Register                         | 02A0h                                 | R/W  |

| 20–21             | MEMBASE                | Non-Prefetchable Memory Base Address              | 0000h                                 | R/W  |

| 22–23             | MEMLIM                 | Non-Prefetchable Memory Limit Address             | 0000h                                 | R/W  |

| 24–25             | PREF_MEM_BASE          | Prefetchable Memory Base Address                  | 0000h                                 | R/W  |

| 26–27             | PREF_MEM_LIM           | Prefetchable Memory Limit Address                 | 0000h                                 | R/W  |

| 28–2B             | PREF_MEM_BASE<br>UPPER | Prefetchable Memory Base Upper 32 bit<br>Address  | 0000000h                              | R/W  |

| 2C-2F             | PREF_MEM_LIM<br>UPPER  | Prefetchable Memory Limit Upper 32 bit<br>Address | 00000000h                             | R/W  |

| 30–31             | IOBASE_HI              | I/O Base Upper 16 Bit Address                     | 0000h                                 | RO   |

| 32–33             | IOBASE_LO              | I/O Limit Upper 16 Bit Address                    | 0000h                                 | RO   |

| Address<br>Offset | Mnemonic   | Register Name               | Default  | Туре |

|-------------------|------------|-----------------------------|----------|------|

| 3C-3D             | INT_LINE   | Interrupt Line              | 00h      | RO   |

| 3E-3F             | BRIDGE_CNT | Bridge Control              | 0000h    | R/W  |

| 40–43             | _          | Reserved                    | 00006801 | R/W  |

| 50–51             | CNF        | P64H Configuration Register | 0000h    | R/W  |

| 70                | MTT        | Multi-Transaction Timer     | 00h      | R/W  |

| 72                | _          | Reserved                    | 00       | RO   |

| 80                | DTT        | Delay Transaction Timer     | 00h      | R/W  |

| 90                | ERR_CMD    | Error Command Register      | 00h      | R/W  |

| 92                | ERR_STS    | Error Status Register       | 00h      | R/W  |

### 2.2.1. VID—Vendor ID Register (D31:F0)

Address Offset: 00-01h

Default Value: 8086h

Attribute: RO

Size: 16 bits

| Bit  | Description                                                           |

|------|-----------------------------------------------------------------------|

| 15:0 | Vendor Identification Number: This 16-bit value is assigned to Intel. |

|      | VID=8086h.                                                            |

### 2.2.2. DID—Device ID (D31:F0)

Address Offset: 02–03h

Default Value: 1360h

Attribute: RO

Size: 16 bits

| Bit  | Description                                                                                            |

|------|--------------------------------------------------------------------------------------------------------|

| 15:0 | Device Identification Number: This is a 16 bit value assigned to the P64H hub interface to PCI bridge. |

|      | ID =1360.                                                                                              |

### 2.2.3. CMD—Device Command (D31:F0)

Address Offset: 04–05h

Default Value: 0000h

Attribute: R/W

Size: 16 bits

| Bit                                                             | Description                                                                                                                                                                                            |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:10                                                           | Reserved                                                                                                                                                                                               |

| 9                                                               | Fast Back to Back Enable (FBE)—RO: This bit indicates whether the P64H is allowed to run cycles originating from hub interface B in fast back to back mode. The P64H does not support this capability. |

| 8                                                               | SERR# Enable (SERR_EN)—R/W: Controls SERR# enable on the hub interface.                                                                                                                                |

| 7                                                               | Wait Cycle Control—RO: Hardwired to 0.                                                                                                                                                                 |

| 6                                                               | Parity Error Response—R/W: Controls the P64H's response when a parity error is detected on the hub interface.                                                                                          |

|                                                                 | 1 = Enable. P64H reports parity errors on the hub interface B.                                                                                                                                         |

|                                                                 | 0 = Disable. P64H ignores parity errors on the hub interface B.                                                                                                                                        |

| 5                                                               | VGA Palette Snoop Enable—RO: Hardwired to 0.                                                                                                                                                           |

| 4 Memory write and invalidate enable (MWIE)—RO: Hardwired to 0. |                                                                                                                                                                                                        |

| 3                                                               | Special Cycle Enable (SCE)—RO: Hardwired to 0 by P2P Bridge specification.                                                                                                                             |

| 2                                                               | <b>Bus Master Enable (BME)—R/W:</b> Controls the P64H's ability to initiate memory transactions on the hub interface on behalf of an initiator on the PCI bus.                                         |

|                                                                 | 1 = Enable. P64H accepts cycles from PCI to be passed to the hub interface.                                                                                                                            |

|                                                                 | 0 = Disable. P64H does not respond to Memory or I/O transactions on the PCI bus and does not initiate I/O or memory transactions on the hub interface.                                                 |

| 1                                                               | <b>Memory Space Enable (MSE)—R/W:</b> Controls the P64H's response to memory transactions on the hub interface.                                                                                        |

|                                                                 | 1 = Enable. P64H responds to memory transactions initiated on the hub interface.                                                                                                                       |

|                                                                 | 0 = Disable. P64H does not respond to memory transactions initiated on the hub interface.                                                                                                              |

| 0                                                               | I/O Enable (IOE)—R/W: Controls the P64H's response to I/O transactions on the hub interface.                                                                                                           |

|                                                                 | 1 = Enable. P64H responds to I/O transaction initiated on the hub interface.                                                                                                                           |

|                                                                 | 0 = Disable. P64H does not respond to I/O transaction initiated on the hub interface.                                                                                                                  |

### 2.2.4. PD\_STS—Primary Device Status Register (D31:F0)

Address Offset: 06–07h

Default Value: 0020h

Attribute: R/WC

Size: 16 bits

For the write-able bits in this register, writing a 1 clears the bit. Writing a 0 has no effect.

| Bit  | Description                                                                                                                                                                          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | Detected Parity Error (DPE)—R/WC:                                                                                                                                                    |

|      | 1 = Indicates that the P64H detected a address or data parity error on the hub interface. This bit will be<br>set even if the Parity Error Response bit is not set.                  |

|      | 0 = The bit is cleared by writing a 1 to the location.                                                                                                                               |

| 14   | Signaled System Error (SSE)—R/WC:                                                                                                                                                    |

|      | 1 = SERR# cycle is initiated by the P64H to the hub interface.                                                                                                                       |

|      | 0 = The bit is cleared by writing a 1 to the location.                                                                                                                               |

| 13   | Received Master Abort (RMA)—R/WC:                                                                                                                                                    |

|      | 1 = P64H as a master on the hub interface receives a master abort from the MCH.                                                                                                      |

|      | 0 = The bit is cleared by writing a 1 to the location.                                                                                                                               |

| 12   | Received Target Abort (RTA)—R/WC:                                                                                                                                                    |

|      | 1 = P64H as a master on the hub interface receives a target abort from the MCH. This bit can be used<br>to generate an internal SERR# (see the ERR_CMD register).                    |

|      | 0 = The bit is cleared by writing a 1 to the location.                                                                                                                               |

| 11   | Signaled Target Abort (STA)—R/WC:                                                                                                                                                    |

|      | 1 = P64H, as the target on the hub interface, signals a target abort.                                                                                                                |

|      | 0 = The bit is cleared by writing a 1 to the location.                                                                                                                               |

| 10:9 | Reserved                                                                                                                                                                             |

| 8    | <b>Data Parity Error Detected (DPD)—R/WC:</b> With the PERR signal removed from the hub interface, the P64H must interpret this bit differently than it is in the PCI specification. |

|      | 1 = This bit is set to 1 when the Parity Error Response bit (CMD register) is set to 1 and the P64H detects a parity error as a hub interface initiator.                             |

|      | 0 = The bit is cleared by writing a 1 to the location.                                                                                                                               |

| 7    | Fast Back to Back—RO: Hardwired to 0.                                                                                                                                                |

| 6:0  | Reserved                                                                                                                                                                             |

#### **2.2.5. REVID—Revision ID (D31:F0)**

Address Offset: 08h

Default Value: See latest Specification Update

Attribute: RO Size: 8 bits

| Bit | Description                                                                 |

|-----|-----------------------------------------------------------------------------|

| 7:0 | Revision Identification Number: Indicates the revision number for the P64H. |

#### 2.2.6. PIF – Programming Interface

Address Offset: 09h

Default Value: 00h

Attribute: RO

Size: 8 bits

| Е | Bit | Description                                                                                |

|---|-----|--------------------------------------------------------------------------------------------|

| 7 | 7:0 | Programming Interface: Indicates that this is a standard (non-subtractive) PCI-PCI bridge. |

#### 2.2.7. SCC—Sub-Class Code Register (D31:F0)

Address Offset: 0Ah

Default Value: 04h

Attribute: RO

Size: 8 bits

| Bit | Description                                                    |

|-----|----------------------------------------------------------------|

| 7:0 | Sub-Class Code: Indicates the category of bridge for the P64H. |

|     | 04h = PCI-to-PCI bridge.                                       |

#### 2.2.8. BCC—Base-Class Code Register (D31:F0)

Address Offset: 0Bh

Default Value: 06h

Attribute: RO

Size: 8 bits

| Bit | Description                                      |

|-----|--------------------------------------------------|

| 7:0 | Base Class Code: Indicates the P64H device type. |

|     | 06h = Bridge device.                             |

#### 2.2.9. CLS—Cache Line Size Register (D31:F0)

Address Offset: OCh

Default Value: 00h

Attribute: RO

Size: 8 bits

| Bit | Description                                                                   |

|-----|-------------------------------------------------------------------------------|

| 7:0 | Cache Line Size Register: The P64H does not perform memory write and invalid. |

#### 2.2.10. PMLT—Primary Master Latency Timer (D31:F0)

Address Offset: 0Dh

Default Value: 00h

Attribute: R/W

Size: 8 bits

| Bit | Description                           |

|-----|---------------------------------------|

| 7:3 | Timer Value: This is not implemented. |

| 2:0 | Reserved                              |

#### 2.2.11. HEADTYP—Header Type Register (D31:F0)

Address Offset: 0Eh

Default Value: 01h

Attribute: RO

Size: 8 bits

| Bit | Description                                                             |

|-----|-------------------------------------------------------------------------|

| 7   | Multi-function Device: Hardwired to 0.                                  |

| 6:0 | Header Type: Identifies the header layout of the configuration space.   |